Dear expert,

More update for below issue:

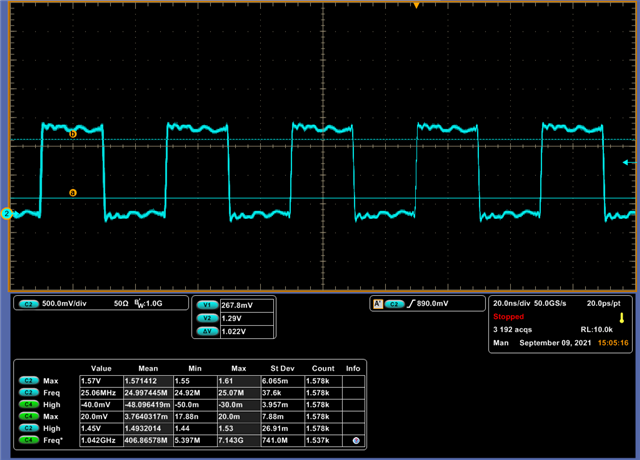

1. External 25MHz ref clock is attached. It is quite stable and good .

2. I find if I reduce external clock frequency, the issue can be better. I continue resume PDB to test. For 25MHz external clock, almost half chance to fail to lock. For 23MHz, there are only 3 failure among 1 hour test. For 22MHz and 21MHz, there are NONE failure among 1 hour test.

3.I checked all power supply. It is clean and within spec. I still doubt this is due to PLL power supply. I don't know which power supply is for PLL. Then I use external linear power supply for VDDL1, VDDL2, VDD18A, VDDIO(1.8V). The phenomenon doesn't change.

Question:

1. Which power pin is for PLL?

2. What might be the reason 21MHz,22MHz(Which is already beyond the spec) works better than 25MHz?

3. Any other suggestion?

Great thanks