Hi Team,

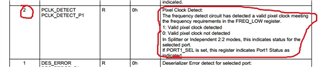

My customer now use 941 (DSI 1920*2*720) and 2*948(1920*720). And found error in 0Ch register D2, PCLK_DETECT will become 0 and then display is abnormal.

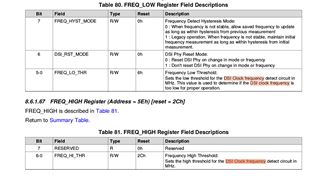

Customer already try to change 0x5D and 0x5E register but still PCLK_DETECT have error.

Could you kindly help to give some advice?

Here are the initialization

{0x0c, 0x01, 0x03, 0},//reset all

{0x0c, 0x01, 0x08, 0},//Disable DSI

{0x0c, 0x1E, 0x01, 0},//Select FPD-Link III Port 0

{0x0c, 0x03, 0x9A, 0},//Enable I2C_PASSTHROUGH, FPD-Link III Port 0

{0x0c, 0x17, 0x9E, 0},

{0x0c, 0x0E, 0x03, 0},

{0x0c, 0x0F, 0x03, 0},

{0x0c, 0x4F, 0x0C, 0},//Set DSI_CONTINUOUS_CLOCK, 4 lanes, DSI Port 0

{0x0c, 0x5B, 0x07, 0},//Force Splitter mode

{0x0c, 0x56, 0x80, 0},//Enable Left/Right 3D processing to allow superframe splitting

{0x0c, 0x32, 0x80, 0},//IMG_LINE_SIZE0 7:0

{0x0c, 0x33, 0x07, 0},//IMG_LINE_SIZE1 12:8

{0x0c, 0x5D, 0x00, 0},

{0x0c, 0x1E, 0x02, 0},//Select FPD-Link III Port 1

{0x0c, 0x03, 0x9A, 0},

{0x0c, 0x17, 0x9E, 0},

{0x0c, 0x4F, 0x0C, 0},//Set DSI_CONTINUOUS_CLOCK, 4 lanes, DSI Port 1

{0x0c, 0x5B, 0x07, 0},//Force Splitter mode

{0x0c, 0x56, 0x80, 0},//Enable Left/Right 3D processing to allow superframe splitting

{0x0c, 0x32, 0x80, 0},//IMG_LINE_SIZE0 7:0

{0x0c, 0x33, 0x07, 0},//IMG_LINE_SIZE1 12:8

{0x0c, 0x5D, 0x00, 0},

{0x0c, 0x1E, 0x01, 0},

{0x0c, 0x36, 0x00, 0},

{0x0c, 0x37, 0x80, 0},

{0x0c, 0x38, 0x7F, 0},//x end 7:0

{0x0c, 0x39, 0x07, 0},//x end 12:8

{0x0c, 0x3A, 0x00, 0},

{0x0c, 0x3B, 0x00, 0},

{0x0c, 0x3C, 0xCF, 0},//y end 7:0

{0x0c, 0x3D, 0x02, 0},//y end 12:8

{0x0c, 0x40, 0x04, 0},

{0x0c, 0x41, 0x05, 0},

{0x0c, 0x42, 0x0C, 0},

{0x0c, 0x1E, 0x02, 0},

{0x0c, 0x36, 0x00, 0},

{0x0c, 0x37, 0x80, 0},

{0x0c, 0x38, 0x7F, 0},//x end 7:0

{0x0c, 0x39, 0x07, 0},//x end 12:8

{0x0c, 0x3A, 0x00, 0},

{0x0c, 0x3B, 0x00, 0},

{0x0c, 0x3C, 0xCF, 0},//y end 7:0

{0x0c, 0x3D, 0x02, 0},//y end 12:8

{0x0c, 0x40, 0x08, 0},

{0x0c, 0x41, 0x05, 0},

{0x0c, 0x42, 0x0C, 0},

{0x0c, 0x30, 0x01, 0},

{0x0c, 0x01, 0x00, 100},