Other Parts Discussed in Thread: ALP

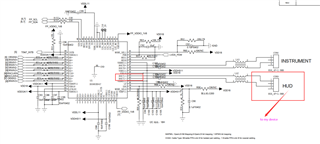

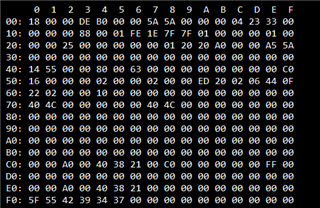

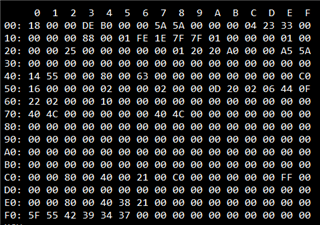

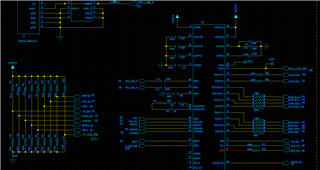

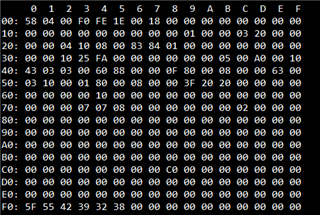

Hello, our device is in the mode of host + HUD. The host outputs serial signals to HUD through 947. HUD uses 928 to deserialize. Now I can light up the screen and see a little bit, but the image cannot be displayed normally, and the flicker is particularly severe . The measurement found that the level of 928 LOCK pin is always changing. After entering the BIST mode, the PASS pin is LOW. Now the problem is that I don’t know where to continue the investigation, so please help to answer it and see where i can start, thank you. In addition, is LOCK always high under normal circumstances?