Other Parts Discussed in Thread: DP83TC811

Dear team,

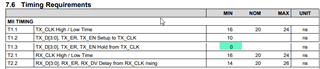

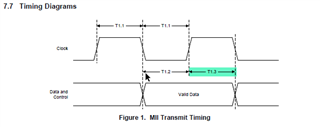

Could you please help me understanding the T1.3 MII Timing in the datasheet ?

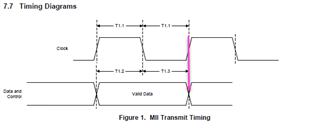

It is mentioned that the minimum hold-time after the TX_CLK is 0ns which seems surprising since it would mean that the data could be transitioning while being sampled by the internal logic circuits of DP83TC811 (see the third picture, where T1.3 has been reduced to 0ns).

How do we guarantee a correct sampling in that case ?

Thank you very much!

Best regards,

PA