Hi TI E2E Expert,

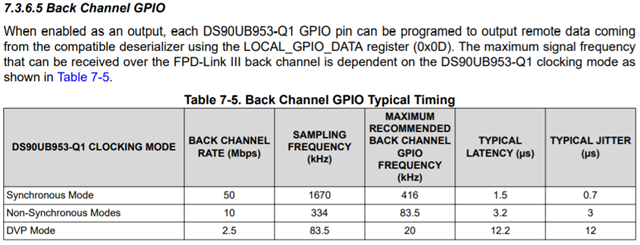

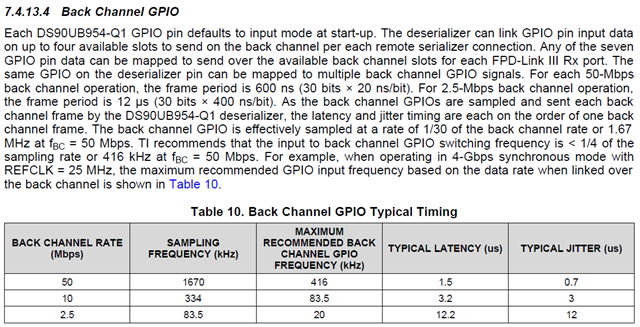

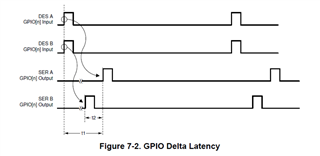

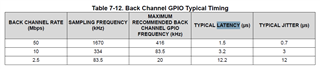

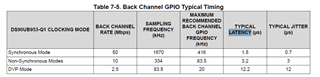

I have a questions about the 954/953 back channel GPIO latency, 1.5us for sync mode, 3.2us for non-sync and 12.2 for DVP.

Why DVP is bigger than non-sync and bigger than sync? could you help explain the reason?

Also have a look at Maxim MAX96705/6, which back channel GPIO latency us 350us, which can be benchmarked with the DVP mode 12.2us.

But 350us and 12.2 us is very big difference? could you help illustrate how to realize it compared with MAX?

Thanks

Best regards,

John