Part Number: DS90UB953-Q1

Hi Team,

There is a good new that DIN DS90UB953TRHBRQ1

1. Please help check this SCH, THX

2. Do we have DS90UB953TRHBRQ1 layout guide line? THX

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: DS90UB953-Q1

Hi Team,

There is a good new that DIN DS90UB953TRHBRQ1

1. Please help check this SCH, THX

2. Do we have DS90UB953TRHBRQ1 layout guide line? THX

Hi Kygo,

I can review your schematic and return with comments within a ~1 week timeline (10/13 at the latest).

And for the layout guidelines, we do have layout guidelines listed in Section 10 of the DS90UB953 datasheet. The UB953's EVM User's Guide can also be referenced. And the partnered Deserializer device's datasheet (DS90UB954/960/etc...) also has more details as well.

Best,

Justin Phan

Hi Justin,

Thank you

1. Also help me confirm that the frequency we give on 954 is 25MHz, so the sensor clk of 953 will also be 25MHz,

Is there a setting for frequency division under 954, so that sensor clk can receive 12MHz?

2. In addition, the 50 ohm single-ended impedance line in the red box is currently 5 mil due to impedance matching. Is it too thick? How much mil does the original manufacturer recommend?

Hi Kygo,

1) Assuming that the REFCLK frequency on the connected UB954 is 25MHz and your devices are in Synchronous Mode, then you can configure the UB953 to output 12MHz on its CLK_OUT pin.

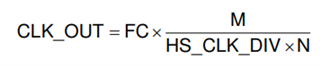

FC - Forward channel line rate. If the REFCLK inputted into the UB954 is 25MHz, then the line rate will be 4Gbps. See the UB954 datasheet for more details.

HS_CLK_DIV, M, and N - parameters set by registers 0x06 and 0x07 in the UB953. The default values will result in a CLK_OUT of 25MHz.

See section "7.4.1.5 Configuring CLK_OUT" in the UB953 datasheet for examples on how to configure a CLK_OUT to about 12MHz. There are potential tradeoffs when selecting the M, N, and HS_CLK_DIV values, in terms of frequency tolerance and jitter. The datasheet explains more with examples.

2) For the single-ended traces at DOUT+ and DOUT-, I recommend also referencing the images and guidelines in the connected deserializer's datasheet. Select a PCB trace width for the DOUT+/- pins that meet the following criteria:

a) Ensure there is tightly controlled 50-Ohms (+/-10%) single-ended impedance. The width depends on the PCB stackup.

b) Ensure the PCB trace is thick enough, such that it can carry PoC current without significant temperature rise (<10degC)

c) Ensure the DOUT+ and DOUT- traces are loosely-coupled (Spacing between traces is >= 3 times their width), up to the connector in order to prevent crosstalk. Using a PCB trace that is too thick would affect required spacing.

Best,

Justin Phan

Hi Kygo,

That's no problem. I will continue to work on the schematic review. In the meantime, let me know if you have any other questions related to this forum post.

Best,

Justin Phan

Hi Kygo,

Here are my comments on the schematic. There are some parts in the schematic that are not shown, so feel free to follow-up if there are any questions.

1) At DOUT+ (Pin 14), do not place a diode behind the AC coupling capacitor. Diodes must be placed on the other side of the AC coupling capacitor and be placed as close to the connector as possible.

2) It is not clear if a PoC network is being used. If it is being used, make sure to use the appropriate 4G or 2G PoC network listed in the datasheet based on the chosen Forward Channel bit rate.

3) On CLKOUT/IDx (pin 19), you need a voltage divider for the IDX functionality. Create a voltage divider at this pin that matches the voltage range for the desired setting in Table 7-9. IDX Configuration Setting in the datasheet. For the CLKOUT functionality of this pin, make sure that the load impedance of the resistors at this pin is >=35-kOhms. This prevents leakage current from affecting the CLKOUT signal. See Table 7-9 for suggested resistors in the datasheet that meet the requirements for both functionality.

4) On VDDD (pin 25), use a set of 1uF and 0.01uF decoupling capacitors.

5) On VDDPLL (pin 11), use a set of 1uF and 0.01uF decoupling capacitors.

6) On VDDDRV (pin 16), use a set of 1uF and 0.01uF decoupling capacitors.

7) The pull-up resistors for the SDA and SCL pins are not shown. Make sure that there are pull-up resistors. The general recommendation is to use between 470-Ohms to 4.7-kOhms pull-up to either 1.8V or 3.3V. Refer to the App Note (SLVA689) linked in the datasheet to calculate the optimal pull-up resistor value for the I2C bus, which depends on the configured I2C data rate and bus capacitance.

8) The voltage divider at the MODE pin (pin 21) is not visible, but since the CLKIN (pin 20) is left open as a Test Point, I will assume that Synchronous Mode has been selected. Make sure the voltage divider at MODE meets the voltage range for Synchronous mode by referring to Table 7-8. Strap Configuration Mode Select in the UB953 datasheet.

9) PDB (pin 8) is not shown. Make sure that there is a delay method implemented there. For normal operation, PDB needs to remain LOW until after the other power supply pins stabilize (See Section 9.1 Power-Up Sequencing in the datasheet for more information). Either use an RC circuit with a 10-kOhm pull-up resistor to VDDIO and a >=10uF capacitor to ground to introduce RC delay. Or use a separate SoC to control when PDB pull HIGH.

Best,

Justin Phan

Hi Justin,

Thank you !

Respond to your suggestions

1.At DOUT+ (Pin 14), do not place a diode behind the AC coupling capacitor. Diodes must be placed on the other side of the AC coupling capacitor and be placed as close to the connector as possible.

>>>TVS201 is currently no use, there is a TVS401 at the source of POC

2.On CLKOUT/IDx (pin 19), you need a voltage divider for the IDX functionality. Create a voltage divider at this pin that matches the voltage range for the desired setting in Table 7-9. IDX Configuration Setting in the datasheet. For the CLKOUT functionality of this pin, make sure that the load impedance of the resistors at this pin is >=35-kOhms. This prevents leakage current from affecting the CLKOUT signal. See Table 7-9 for suggested resistors in the datasheet that meet the requirements for both functionality.

>>>The voltage divider circuit of IDX is as follows, please confirm it ,THX

3.The pull-up resistors for the SDA and SCL pins are not shown. Make sure that there are pull-up resistors. The general recommendation is to use between 470-Ohms to 4.7-kOhms pull-up to either 1.8V or 3.3V. Refer to the App Note (SLVA689) linked in the datasheet to calculate the optimal pull-up resistor value for the I2C bus, which depends on the configured I2C data rate and bus capacitance.

>>>I2C pull high resistance is as follows, please confirm

4.Could you help review customer's PCB layout of DS90UB953-Q1? THX

Hi Kygo,

I also see that a PoC circuit is being implemented that does not match the recommended 4G PoC circuit used in the datasheet. Customers can use their own custom PoC circuit, but it will be up to them to verify that the PoC circuit meets the requirements. The PoC circuit should provide >=2-kOhms impedance over the Nyquist frequency range of the channel's selected bit rate. We have a recommended PoC circuit for Synchronous mode (See Figure 8-2. Typical PoC Network for a "4G" FPD-Link III in the UB953 datasheet), which works using the suggested components in Table 8-1 at a DC bias current of up to 150mA.

Best,

Justin Phan

Hi Kygo,

Layout review will be conducted offline. I will close this thread for now.

Best,

Justin Phan