Hi Team,

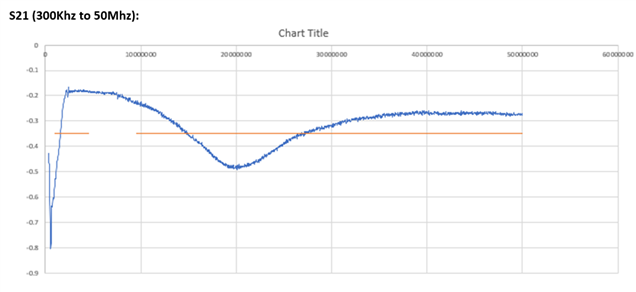

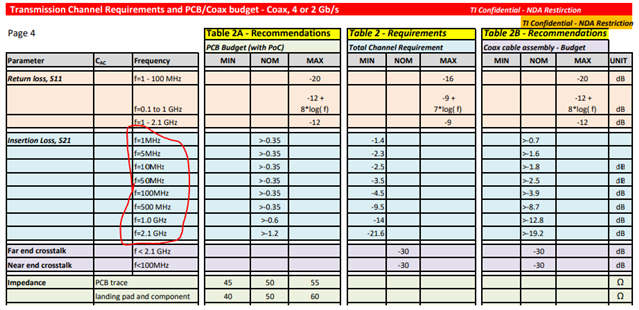

Could you please clarify the the insertion loss for Total channel requirements and Cable assembly at 15Mhz, 20Mhz, 25Mhz?.

I'm not sure If I should use the f=50Mhz number, f=10Mhz number, or assume there is a linear relationship and go somewhere in-between.

Best,

David