Below attached images has our SFP architecture.

1. In Our design we are using two DS250DF230. One for TX section and another for RX section of the SFP (We are having 2 SFP ports)

As per the datasheet "It is generally recommended that channels connected to the same front-port cage be grouped together in the same DS250DF230 device" is this mandatory, With this configuration TX and RX Re-timer cannot be placed near the receiving section.

2. Can we Place the Re-timer as mentioned in the image. TX Re-timer near the SFP connector and RX Re-timer near the FPGA.

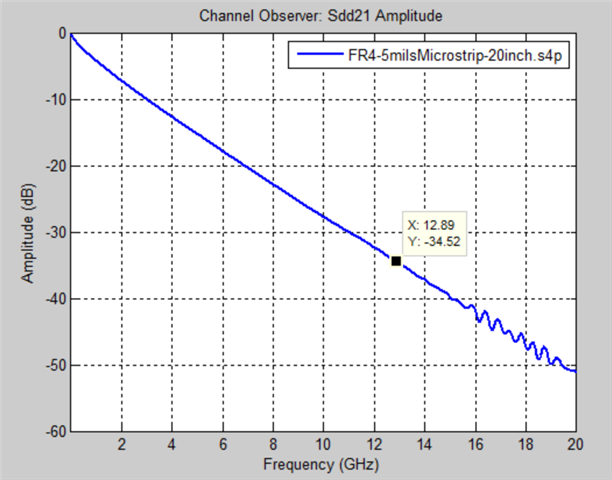

3. How to calculate the losses due the trace length. what is the formula to calculate those loses.