Hi team,

Now my customer has a 947-940N system and has encounter some problems.

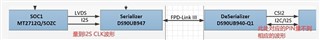

SoC1 sends out I2S----->947----->940----->SoC2 receives I2S---->car audio equipment,

Q1. Does 947 need to configure any registers in 940N to get the I2S signal at 940N output?

Q2. Could 940N side SoC be the master and 947 side SoC be the slave? This is customer expired master-slave mode configuration and if so please tell us how to configure SER and DES to be the proper master-slave settings.

Detail descripts:

System block diagram

(The red words on the left mean could test the I2S signal at 947 input while the right read words mean could not test the test I2S at 940N output)

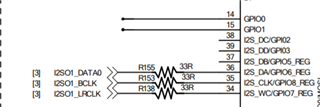

Hardware info-

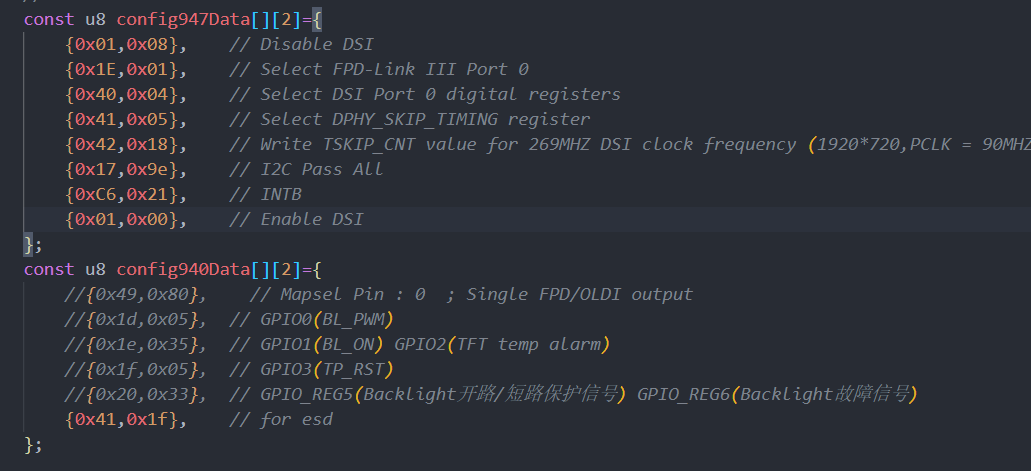

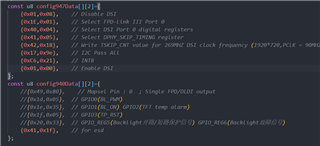

Software info- Here is the register configuration of 947 and 940N:

In my opinion it should be configured from 947 side rather than 940N side right? What other registers should be configured in 947 or 940N?

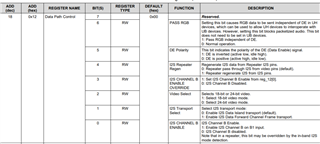

I also have questions about this 0x12 register, in our system block diagram, how could we configure this register and what does the 'I2S channel B' mean?

The 947 has already accessed the 940N so I think the LVDS link has been successfully established and besides that could we test the I2S between SER and DES?

Hope to hear from you soon, thank you.