Other Parts Discussed in Thread: DLPC230-Q1

Dear TI Teams,

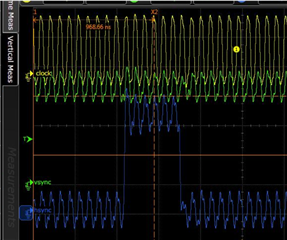

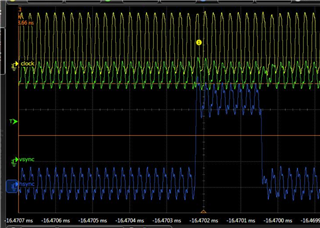

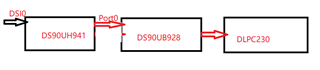

I use DS941 with single mode, input: DSI0, output:port0, as follow,

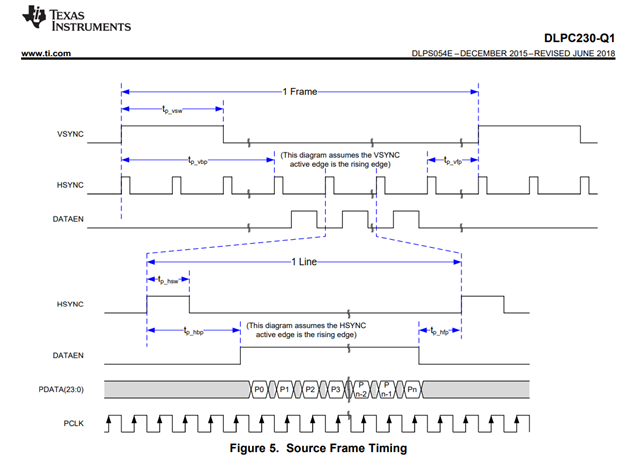

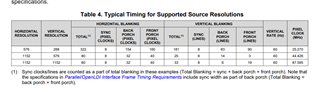

Use DLPC230 resolution size:1152x576

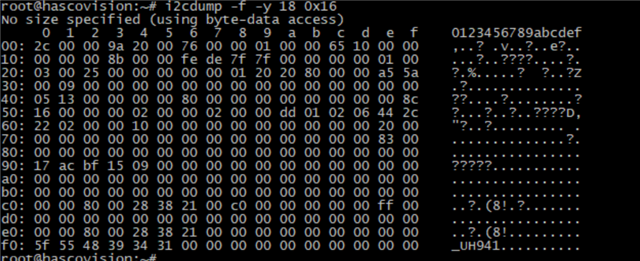

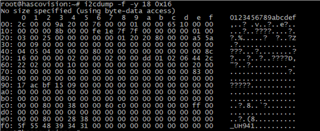

1. My ds941 test code:

i2cset -f -y 18 0x16 0x01 0x08

i2cset -f -y 18 0x16 0x1E 0x01

i2cset -f -y 18 0x16 0x03 0x9A

i2cset -f -y 18 0x16 0x04 0x20

i2cset -f -y 18 0x16 0x1E 0x01

i2cset -f -y 18 0x16 0x40 0x04

i2cset -f -y 18 0x16 0x41 0x21

i2cset -f -y 18 0x16 0x42 0x60

i2cset -f -y 18 0x16 0x5B 0x01

i2cset -f -y 18 0x16 0x4F 0x8C

i2cset -f -y 18 0x16 0x40 0x04

i2cset -f -y 18 0x16 0x41 0x05

i2cset -f -y 18 0x16 0x42 0x04

i2cset -f -y 18 0x16 0x01 0x00

2. In software DLPC230 Control Program 1.9 Build 1260, output error:

Error Code:Source Error(0x3B2)-Expected VSYNC singal did not arrive in the time allocated.

How can fix this error? Thanks.