Part Number: DS90UB934-Q1

Other Parts Discussed in Thread: USB2ANY

Hi Team,

My customer found 933/934 I2C communication failure in production. While LOCK/PASS is ok. 933 address is 0xB0.

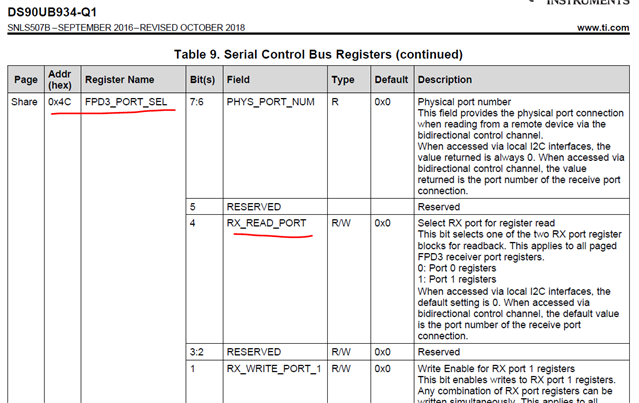

When read 0x5B(SER_ID) in abnormal 934, it returned 0x00. In normal device, SER_ID is 0xB0. Here we want to double confirm this SER_ID fundamental with you:

1. How does 933 load SER_ID to 934 during start up?

2. Is there sequencing(or others) requirement of the 933/934 system to let the SER_ID loading successfully?

3. If loading failed(SER_ID=0x00), will it cause the I2C communication failure?

4. Can customer write SER_ID by manual to link the 933?

Can you please help comment at your earliest convenience since it is an urgent case in my customer and Car OEM.

Many thanks.

BR,

Rory