Dears,

We encounter a problem on a custom design using the PHY Ethernet DP83848-EP.

At power on, when an Etherent cable is connected, even when the PC connected at the other side doesn't send any frame, there is a signal on RXD1 and CRC of the RMII bus.

To avoid any potential problem from external component, we have connected the PHY from one side to the transformator & connector RJ45, and to the other side (RMII), to nothing (we cut the line for tests). There are two case:

1- the PC doen't send any data (check with wireshark) -> the parasite signal is present

2- the PC send data -> our data are present with the parasite signal

It looks like we are in a failure mode.

We test to change the registers without effect. We cut the MDIO line, without effect. Here is the scheme and some screenshot of the "parasite" signal.

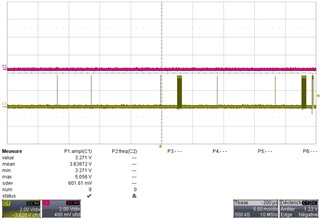

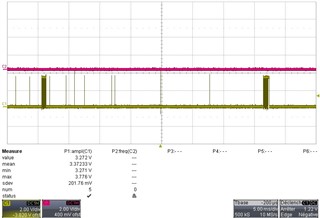

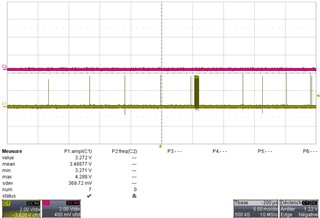

Its main characteristics are:

- there are "little communication" and "big communication"

- No period have been identified

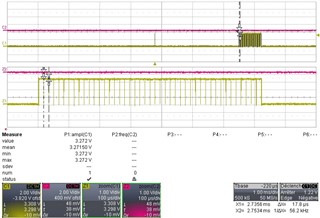

- "big communication" are ~720 µs large nearly all bits are 1 and ~43 periodic bits are 0

Another interesting point is :

- when I send my data each 5 ms, I lose some unitary frame and packet of 15 frames

- when I send my data each 10 ms, I lose some unitary frame and packet of ~7 frames

- when I send my data each 2.5 ms, I lose some unitary frame and packet of 30 frames

--> the PHY seems to "sleep" sometime ~75 ms

Has anyone experiment such a problem, an idea of the mode in which we are, or a solution?

Best regards,

Benjamin