Part Number: SN65DPHY440SS

Hello,

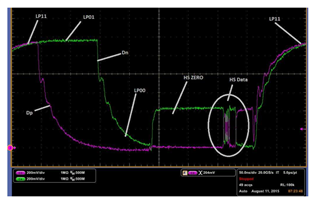

Our customer met a question about SNx5DPHY440SS.Whent the sensor MIPI is non-continue mode, the platform receive MIPI normally.

But when the sensor MIPI is continue mode, the platform receive MIPI abnormally. He configured the register as following, when the receive data is abnormal.

(Address, Data)

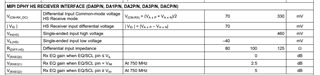

(0x50, 0x10), // HS TX path Override enable

(0x51, 0x10), // HS TS path enable

(0x61, 0x0F), // Disable LP path.

(0x70, 0x10), // HS RS path Override enable

(0x71, 0x10) // HS RX path enable

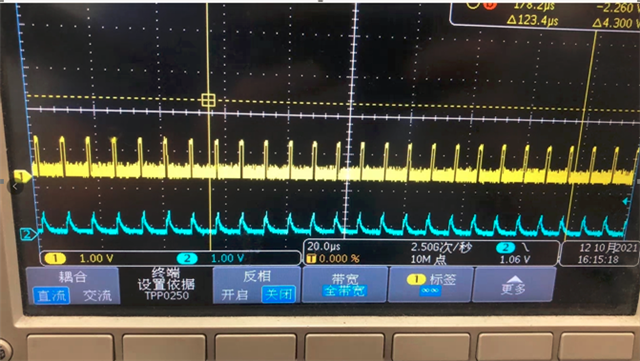

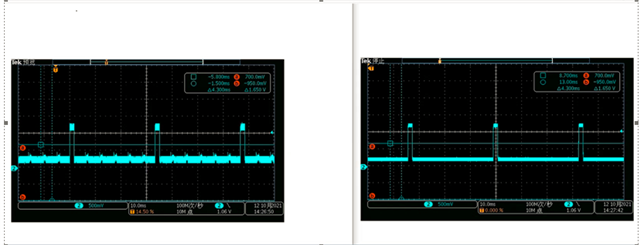

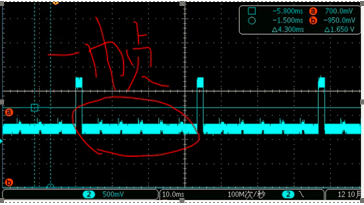

Yellow is input, and blue signal is output, it could be found that the data lane is abnormal.

Best regards

Kailyn

(note:

(note: