Other Parts Discussed in Thread: MIO

Hello everyone,

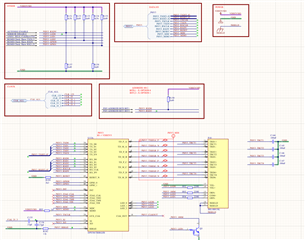

We have a new project that uses Xilinx Zynq 7000 (XC7Z010) processing logic RGMII driver connected to DP83867IRRGZ PHY.

We use this combination in few other projects as well. However in the new project there is (I believe) a problem with the RGMII interface.

This problem is related only to 1G (RGMII). 100M (RMII) always works well.

There are also 2 DP83867IR's on the board fed from the PL (FPGA) part of the Zynq which always work at 1G without any problem.

We receive valid data from the outside PHY3_RXDx, but transmitted data caught by the wireshark are not valid. There is some random data only. Thus I

suspect RGMII TXD part of the interface is not working correct.

Some basic facts about the PCB:

1) Zynq connected to 3 identical PHY's DP83867IRRGZ

2) PHYs on the PL are working at 1G no problem

3) PHY on PS part works at 100M no problem, but at 1G not working

4) We have different boards with similar configuration where PS PHY works at 1G. But there are shorter RGMII traces. Similar stackup.

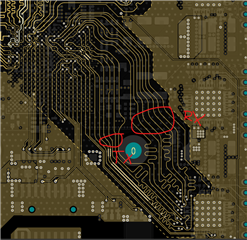

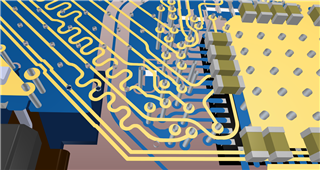

5) RGMII traces are routed at 50ohms (+-10%) impedance profile. This is provided by Simbeor plugin of Altium. Vias are also calculated to 50ohms.

6) RGMII traces are length matched. TX group length is 58.8mm (+-0.1mm), RX group length is 56.3 (+-0.05mm).

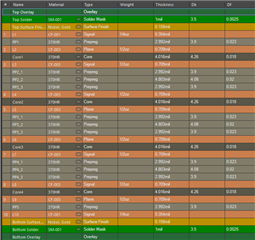

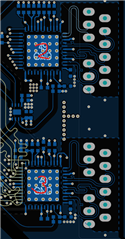

7) All RGMII signals are routed on the layer 3 of the 10 layer PCB. Zynq is on L1, PHY on L10. L2 is a huge ground plane to provide solid return path.

8) The RGMII traces are routed from the ball of the Zynq BGA on L1 to L3, then continue in L3 close to PHY, goes through via to L10. Then connects to the PHY:

9) We tried to route the traces as far of each other as possible to minize crosstalk. There are no series nor parallel termination resistors.

10) General rule of thumb is 6 inch max for RGMII. We are one third roughly so length should be OK. However it might not be true as on our similar board with PHY3 closer to the Zynq 1G works.

11) PCB Stackup - 10layer

12) MDI is not the problem as exactly the same layout is used on the 3 PHYs (and those 2 on PL work well at 1G):

13) No matter which combination of PS MIO speed (slow/fast) PU/PD on Zynq and RGMII delay on PHY we use. It never works correctly.

14) We even tried terminating the RGMII TX line (TXD1,2,3,4, CLK) at the end - near PHY with parallel termination resistors (120R, 100R, 49,9R). Nothing helped

15) Using 200MHz scope we are able to see some data on the RGMII lines, so it is not completely dead. However it does not have enough bandwidth to do deeper research.

Do you have any suggestions what could help?

Thank you.