Part Number: DP83869HM

Other Parts Discussed in Thread: AM6442, DP83869

Hi,

I have a custom board with a AM6442 CPU and a DP83869HMRGZT phy in address 0, which was designed in reference to the TMDS64GPEVM, and was reviewed by TI's team.

The software (Linux) is based on 08.00.00.004 SDK.

The phy's reset signal is connected to a CPU IO and has a pulldown.

The board has a reset button, which resets the CPU (PORz).

The phy reset is released in U-boot, the GPIO is driven to '0' for 10 ms, then up to '1'.

Now, every time I disconnect and connect the power to the board, the phy is identified as DP83869 and I have no problems.

The same is true with "reset" command on u-boot, after this command, the phy is always identified as DP83869.

The problem is with the reset button, after some resets using the button, the phy is identified as "Generic PHY".

Once it is identified as "Generic PHY", it will be identified that way (even with reset command), until I disconnect and reconnect the power to the board.

This can happen after 2-3 resets, and after 20-30 resets.

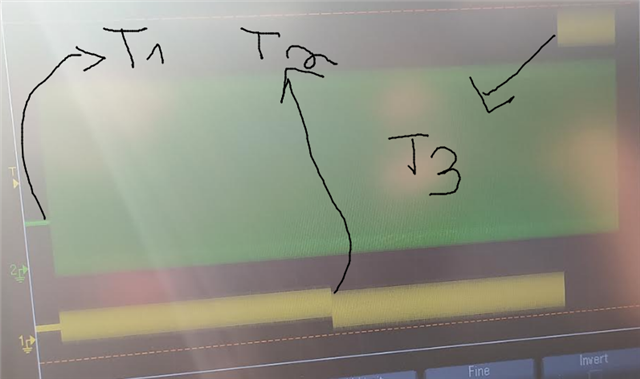

I extended the phy reset duration to 500ms on '0', then wait 500ms on '1', then resume the u-boot code (reset line is kept '1'), and verified that the reset voltage levels are ok.

This is not a phy address issue, even when it is identified as "Generic PHY", it is detected on address 0 (I changed the address with a GPIO write, and nothing was found on this address):

=> mdio list

ethernet@8000000:

0 - Generic PHY <--> ethernet@8000000

=> mii info

PHY 0x00: OUI = 0x1E525E, Model = 0x14, Rev = 0x09, 100baseT, FDX

When the PHY is identified as "Generic PHY", all the registers values are: 0x7949, even the phy ID registers.

The MDIO line has a 2.2KOHM pullup to 3.3V.

This phy is the only device on this mdio bus.

The phy clock source (XI) comes from the CPU's clkout0 signal (25MHz), and is set before the phy reset during U-boot.

Maybe you know how can I debug this issue?

Thanks