Part Number: SN65DP159

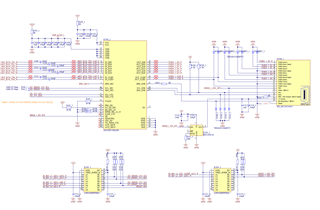

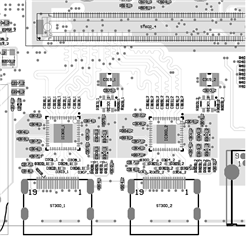

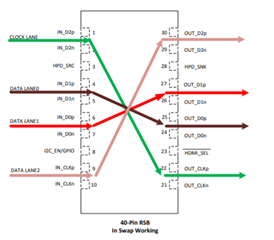

We are using the DP159 in two Designs, connected to an Xilinx FPGA, as a transmitter to a monitor.

The problem is, we have a few monitors working very well and a lot of monitors we can not get to work properly.

The DP159 has a lot of registers and functionality, but exactly that makes it very hard for us to find a good setup. What we need is some kind of instruction for setup and trimming the chip to work with most of the monitors. If this is not possible, we need an instruction how to configure the monitors individual.

So I can separate my request in two questions:

- Is there an optimal setup to get the DP159 working with most of the monitors, and how should the registers be configured, therefore? (maybe some kind of register map with optimal values)

- How should we proceed a trimming of the DP159 by testing it with different register values to get an individual monitor to work?