I try to light up a ti pannel (ds90ub941as + ds90ub948), config the panel in bistmode,

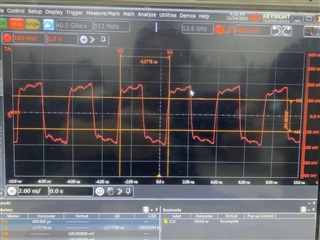

but find 941 can not detect dsi clk, the clock exists actually. please give me some debug advice,thanks.

The follow is init code:

//941 dsi input config(Single-DSI mode,Select DSI Input port 0,4 Lanes)

TiSerdes_I2C_Write_Mask(ti941_addr, 0x4F, 0x0C, 0x6C);

//941 Dual FPD-Link III mode (Single, Dual, or Replicate)

TiSerdes_I2C_Write_Mask(ti941_addr, 0x5B, 0x3, 0x07);

uint8_t value = 0;

value = dm_i2c_reg_read(ti941_addr, 0x06);

TiSerdes_I2C_Write(ti941_addr, 0x17, 0x9e);

TiSerdes_I2C_Write_Mask(ti948_addr, 0x34, 0x8, 0x18);

TiSerdes_I2C_Write_Mask(ti948_addr, 0x49, 0, 0x03);

TiSerdes_I2C_Write(ti948_addr, 0x1f, 0x09);

dm_i2c_reg_write(ti941_addr, 0x64, 0x07);

dm_i2c_reg_write(ti941_addr, 0x66, 0x03);

dm_i2c_reg_write(ti941_addr, 0x67, 0x02);

dm_i2c_reg_write(ti941_addr, 0x66, 0x04);

dm_i2c_reg_write(ti941_addr, 0x67, 0xf8);

dm_i2c_reg_write(ti941_addr, 0x66, 0x05);

dm_i2c_reg_write(ti941_addr, 0x67, 0xe7);

dm_i2c_reg_write(ti941_addr, 0x66, 0x06);

dm_i2c_reg_write(ti941_addr, 0x67, 0x33);

dm_i2c_reg_write(ti941_addr, 0x66, 0x07);

dm_i2c_reg_write(ti941_addr, 0x67, 0x80);

dm_i2c_reg_write(ti941_addr, 0x66, 0x08);

dm_i2c_reg_write(ti941_addr, 0x67, 0x07);

dm_i2c_reg_write(ti941_addr, 0x66, 0x09);

dm_i2c_reg_write(ti941_addr, 0x67, 0x2d);

dm_i2c_reg_write(ti941_addr, 0x66, 0x0A);

dm_i2c_reg_write(ti941_addr, 0x67, 0x28);

dm_i2c_reg_write(ti941_addr, 0x66, 0x0B);

dm_i2c_reg_write(ti941_addr, 0x67, 0x0a);

dm_i2c_reg_write(ti941_addr, 0x66, 0x0C);

dm_i2c_reg_write(ti941_addr, 0x67, 0x28);

dm_i2c_reg_write(ti941_addr, 0x66, 0x0D);

dm_i2c_reg_write(ti941_addr, 0x67, 0x32);

dm_i2c_reg_write(ti941_addr, 0x65, 0x04);

dm_i2c_reg_write(ti941_addr, 0x64, 0x35);

dm_i2c_reg_write(ti941_addr, 0x17, 0x9e);

dm_i2c_reg_write(ti948_addr, 0x1f, 0x09);

941 reg dump:

34 00 00 9a 00 00 58 00 00 01 06 00 63 30 00 00

00 00 00 8f 00 00 fe 9e 7f 7f 01 00 00 00 01 00

0b 00 25 00 00 00 00 00 01 20 20 a0 00 00 a5 5a

00 09 00 05 0c 00 00 00 00 00 00 00 00 00 81 02

10 90 00 00 00 00 00 00 00 00 00 00 00 00 00 8c

16 00 00 00 02 10 00 02 00 00 12 03 07 06 44 00

22 02 00 00 35 04 0d 32 00 00 00 00 00 00 20 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 7f 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 82 00 78 00 00 44 40 00 00 00 00 02 ff 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 82 00 68 08 00 00 00 00 00 00 00 02 00 00

5f 55 42 39 34 31 00 00 00 00 00 00 00 00 00 00