Part Number: SN65LVDS33

Hello,

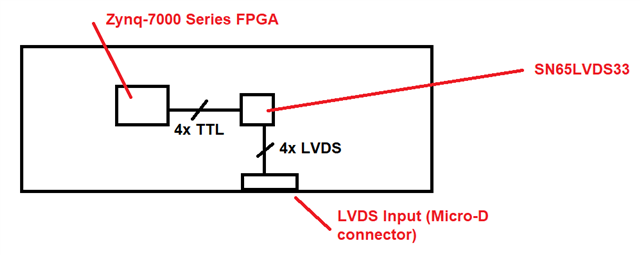

We are using SN65LVDS33 to transmit 4 LVDS signals: CLK, D0, D1, and D2.

The CLK is being run at 100 MHz.

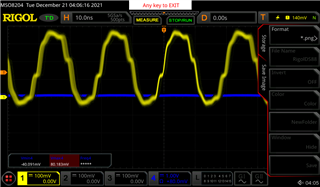

When any 2 of the 3 data channels are enabled (e.g., D0 & D1, or D0 & D2, or D1 & D2), the CLK signal integrity (SI) at the output of the receiver (i.e., the single ended side) is satisfactory.

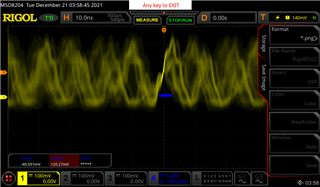

When all 3 data channels are enabled (i.e., D0, D1, and D2), the CLK SI of the single ended signal deteriorates, and worsens as more signal edges are added to the data pattern being transmitted. The CLK SI at the input side (i.e., the LVDS side) remains good.

For example, if the data pattern being transmitted on all channels is 0x2222 (see image below on the left) or 0x4444 (see image below on the right), the CLK SI is good.

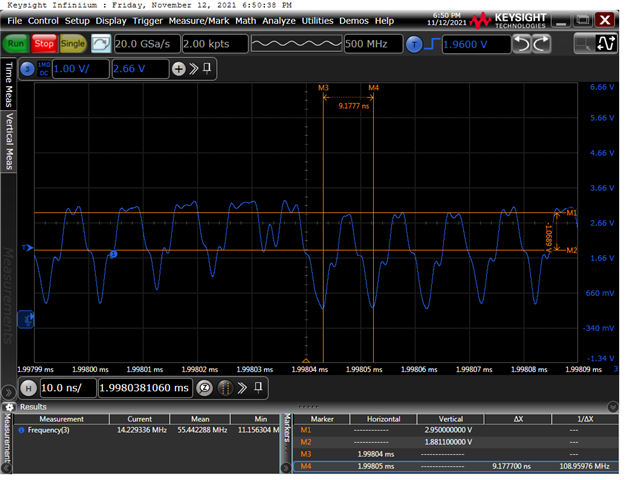

If more signal edges are added to the data pattern, e.g., 0xA9A9, the CLK SI deteriorates to the point where some cycles are missed. See image below.

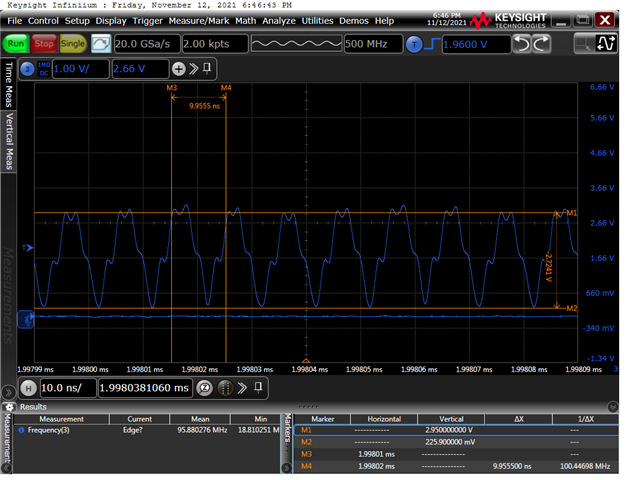

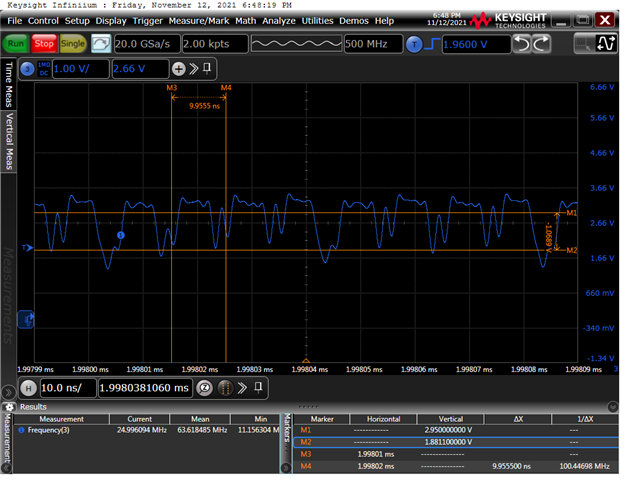

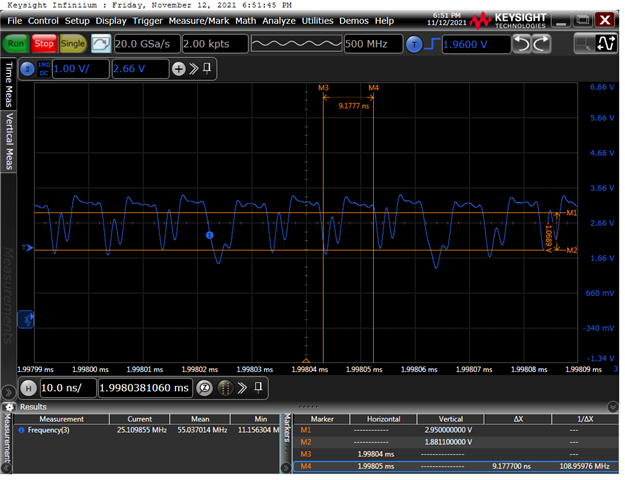

If a data pattern with constantly changing bits is transmitted, e.g., 0x5555 (image below on the left) or 0xAAAA (image below on the right), the CLK stops swinging to 0V and becomes unusable.

Are we pushing the SN65LVDS33 chip beyond its capabilities?

All signals on the LVDS side are good. Traces are routed with the correct impedances, though they are longer than recommended by the TI app notes for LVDS signals.

Note that if we run the CLK at 50 MHz instead of 100 MHz, the CLK SI remains good across all cases.

Any feedback and/or suggestions would be appreciated.

Thanks,

Aki