Hi,

This is in continuation of the below ticket raised earlier as we haven't received a solution yet.

This design is done consulting TI forum (ref: https://e2e.ti.com/support/interface-group/interface/f/interface-forum/531662/xaui-to-10gbase-kr-repeater-de-mux-implementation-using-tlk10232) and we are facing some challenges in getting the design up and running as indicated in the former ticket.

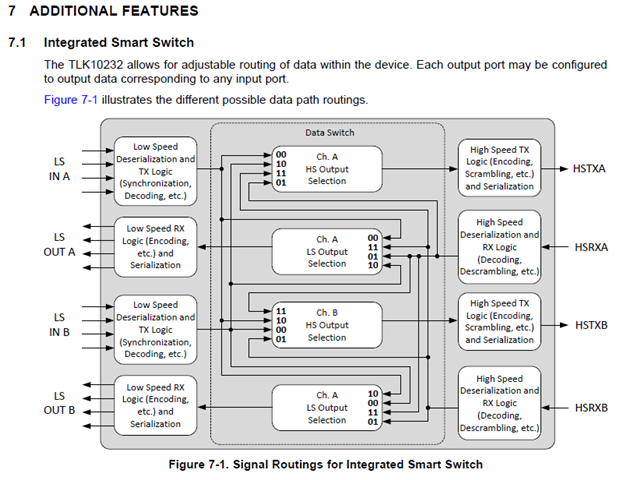

If TI team is not able to replicate the scenario with eval boards, can the tech support team confirm the functionality of the device TLK10232 with respect to our intended mode of operation (High-level mode of operation required is repeated again below for your reference),

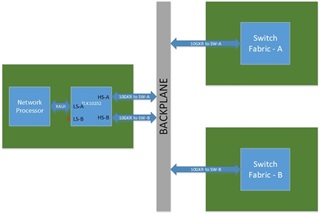

LS -A <--> HS-A, LS-B & HS-B floating/not connected.

and switch to LS-A <--> HS-B, LS-B & HS-A floating/not connected based on PIN level or MDIO software configuration

LS Side is XAUI

HS Side is 10GBASE-KR

Regards,

Jaison