Part Number: SN65DSI86

I would like to ask some problems about how to send SDP pattern by SN65DSI86...

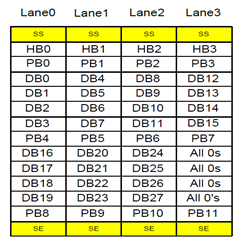

I want send a SDP packet with Header = HB0, HB1, HB2, HB3 and Data = DB0 DB1 DB2 DB3 DB4 DB5 DB6 DB7

According to spec, I should embed this SDP data in Vertical Blanking Time.

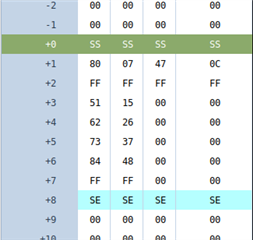

so, I build a MIPI Generic Write Packet in VBP first line with follwing data:

0x29 0x12 0x00 ECC 0x00 0x80 HB0 HB1 HB2 HB3 PB0 PB1 PB2 PB3 DB0 DB1 DB2 DB3 DB4 DB5 DB6 DB7 PB4 PB5 CRC_L CRC_H

However, it does not work.

Can you provide some suggestion or more detailed cotrol flow about SDP?

And hould I build SDP pattern in Left Port or Right Port or Both if my DSI environment is 2 port?

Thank you very much