Other Parts Discussed in Thread: SN65DSI84

We are debugging a 1920*1088 screen with SN65DSI84, now the Colorbar is displayed, and the normal mode is abnormal.

We suspect that there are some problems with the screen parameter or the configuration of the chip itself.

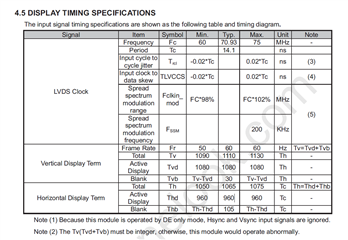

1.This is screen Timing

2. Dsi is now 40fps, the parameter configuration:

sn65dsi84,on-command-1080p = [09 01 10 /* <reg value wait(ms)> */

0a 03 00

0b 28 00

0d 00 10

10 26 00

11 00 00

12 3b 00

13 00 00

18 6c 00

19 00 00

1a 03 00

1b 00 00

20 80 00 /* width-l(a) */

21 07 00 /* width-h(a) */

22 00 00 /* width-l(b) */

23 00 00 /* width-h(b) */

24 38 00 /* height-l(a) */

25 04 00 /* Height-h(a) */

26 00 00 /* height-l(b) */

27 00 00 /* height-h(b) */

28 c8 00 /* sync delay low(a) */

29 00 00 /* sync delay high(a) */

2a 00 00 /* sync delay low(b) */

2b 00 00 /* sync delay high(b) */

2c 2c 00 /* hpw-l(a) */

2d 00 00 /* hpw-h(a) */

2e 00 00 /* hpw-l(b) */

2f 00 00 /* hpw-h(b) */

30 05 00 /* vpw-l(a) */

31 00 00 /* vpw-h(a) */

32 00 00 /* vpw-l(b) */

33 00 00 /* vpw-h(b) */

34 94 00 /* hbp(a) */

35 00 00 /* hbp(b) */

36 24 00 /* vbp(a) */

37 00 00 /* vbp(b) */

38 58 00 /* hfp(a) */

39 00 00 /* hfp(b) */

3a 04 00 /* vfp(a) */

3b 00 00 /* vfp(b) */

3c 00 00 /* bit4 channel a test pattern; bit0 - channel b test pattern */

3d 00 00

3e 00 00

09 00 10

0d 01 05];

Please help to give us some guidance, thank you!