Hi team,

My customer has encountered a strange issue:

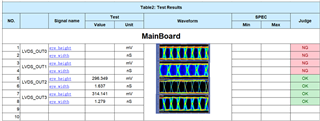

During the eye-diagram test, the LVDS output 0 and output 1 have very poor eye-diagram which are NG:

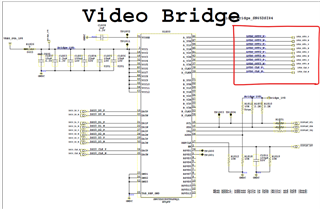

The strange thing is the output content is normal without issue and here is customer's schematic design:

Please kindly help to analyze the issue and tell us why the eye-diagram is poor, this not only happened on single chip but other chips also have the similar phenomenon that LVDS 0 and LVDS 1 have poor eye-diagram with normal display, thank you.