Part Number: TUSB8042A

TUSB8042Aの電源投入、クロック入力タイミング、パワーダウンシーケンスについて教えてください。

我々の回路構成は、水晶発振器(1.8V_CMOSを用いてXIの入力端子に入力するように構成されている。

【質問1】

データシートに「図 1 の電源投入タイミング要件」について質問があります。

GRSTzがコンデンサにGNDに接続されている場合、図1の「VDD→VDD33」のパワーアップシーケンスを満たす必要があります。

ただし、VDDとVDD33が安定した後にGRSTzがデサートされた場合、VDDとVDD33のパワーアップシーケンスを要求することなく、順不同で起動することは可能ですか?

(VDD→VDD33またはVDD33→VDDの順序)

[質問2]

VDDとVDD33が安定する前に、水晶発振器からXI端子にクロックを入力しても大丈夫ですか?

XI端末ですが、電源が供給されていない場合に入力を行うとラッチアップが発生しますか?

[質問3]

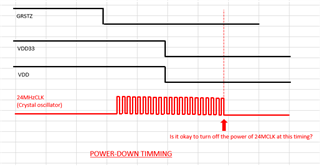

電源ダウンシーケンスについて教えてください。

電源を切る場合、XI端子の水晶発振器を停止した後、VDDとVDD33の電源を切ることをお勧めしますか?