Hi Team,

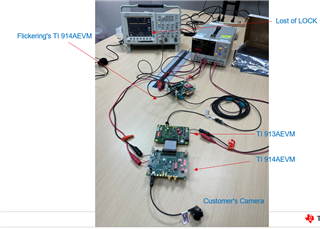

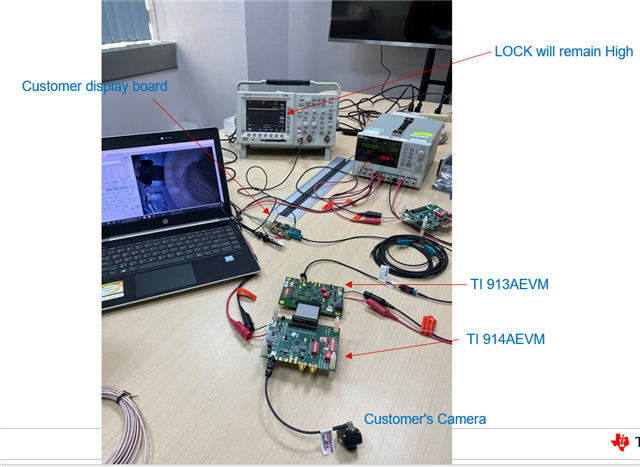

There is a good new that we DIN DS90UB914A-Q1

And there have one thing need your support!

We have check customer’s oToCAM204 camera module & cable , It seems no fail in those test.

What else do we need to verify to prove the problem on the customer's system?

Do we have guideline of verifying the 913 end of the customer's system?

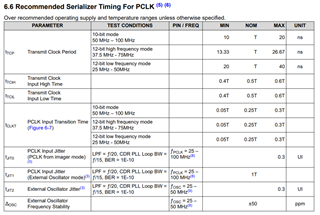

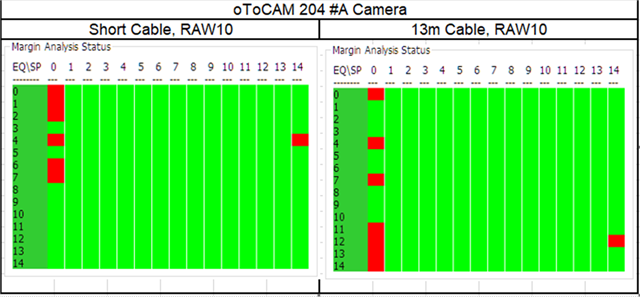

- Margin Analysis could meet spec

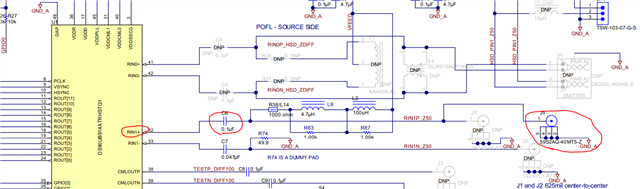

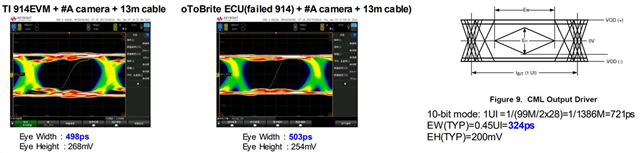

- 914 CML output and the EW/EH meets the criterial refer to datasheet

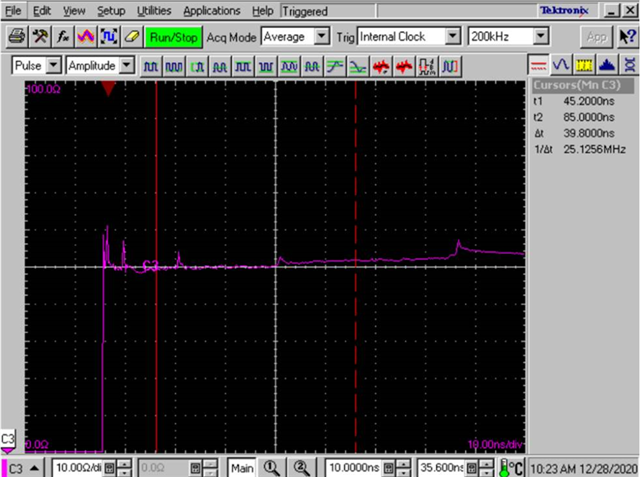

- Cable TDR measure within 50ꭥ±10%

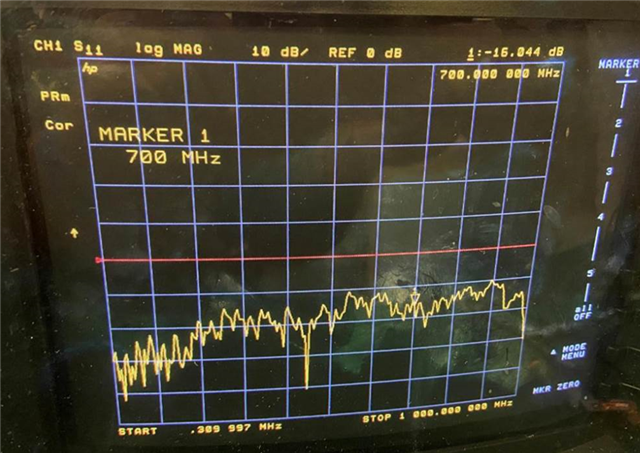

- Cable return loss at 700MHz is -16dB

Margin Analysis

914 CML output

TDR measure

Return loss

Thank you