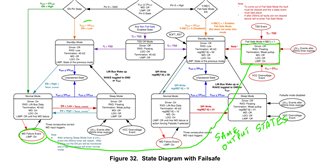

there was a question raised about the state of the LDO output when a WD Failure Event occurs.

I need help to confirm the 2 highlighted assumptions in this email.

Our product concept assumes that the LDO is turned off when a WD Failure Event occurs, but the language in the datasheet is not explicit on this matter.

In addition, I think we have a concern based upon the following assumptions from the datasheet:

- A ‘WD Failure Event’ occurs when the error counter which is the value of the WD_ERR_CNT register reaches the watchdog trigger event level which is the value of the WD_ERR_CNT_SET register.

- The watchdog error counter will increase by 1 every time a WD window is missed.

- When the device is used in Pin Mode, based on the default value of b0100 in the WD_ERR_CNT register at h14[4:1], the error counter is set at four.

- When the device is used in Pin Mode, based on the default value of b10 in the WD_ACTION register at h13[1:0], the nWDR output will toggle from high to low to high every time a WD window is missed.

- When the device is used in Pin Mode, based on the default value of b00 in the WD_ERR_CNT_SET register at h13[3:2], the device will have a ‘WD Failure Event’ on the first missed WD window.

We need to run this device in Pin mode and we currently have the WDT input pulled to ground which sets the watchdog service interval (twindow = Open+Closed windows) at a nominal of 40 ms with a nominal open window of 20ms.

So if assumption #5 is true, then that seems to be pretty stringent.

This means the micro cannot miss a single window during operation.