May I have a requirement(Spec) of rise time for REST_N signal.

How much is the rise time spec.

BestRegards

Kosaka

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

May I have a requirement(Spec) of rise time for REST_N signal.

How much is the rise time spec.

BestRegards

Kosaka

We dont have a rise-time spec for this signal as this is a level based signal.

--

Regards,

Vikram

Hello Vikram

We tried other rise time 0.42ms. It is able to work LED.

So we would like to clear the reset_N signal Logic(Spec) in the LSI.

Edge trigger or Level Trigger? And rise time spec.

Regards,

Kosaka

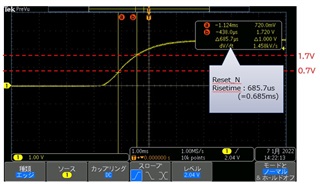

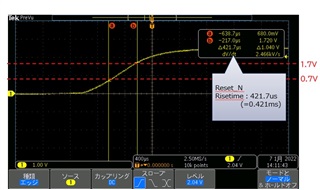

We share the waveforms. And remesure at Low voltage and highvoltgae timing.

LED NG case.

LED OK Case.

Could TI judge the LSI spec from this waveform?

Regards,

Kosaka

Hello,

Looking at the waveforms shared standalone, I dont see a problem with reset rise/time. May be it has to do something with the moment you are toggling resetn. To understand that can you share what LED functionality is being looked at? Is it something related to straps? Does this reset toggling happening at time of power up or later?

Hello

LED is Kept on lighting.

We don't chnage the strap.

It occured at power up. And we read register that wrere all F.

Regards,

Kosaka

Hello Kosaka-san,

I did not get what was the desired functionality of LED. But I understand that when you observe a little slower reset, you also read all F. Is that correct? Do you also have snapshot of the supply of the PHY in the bad case? May be it has something to do with the way supply is ramping and not the reset (as you mentioned that reset is toggling at same time as power-up). Do you see a flat region in the supply ramp or slow ramp of supply voltage?

As a work-around, can you try toggling reset one more time after the supply is stable and may be it will recover the PHY with this extra reset outside the power ramp period.

--

Regards,

Vikram

Hellow Vikram-san

The Register value is all F means an accsess time ou for phy. This mean Phy can not reply read So LED configration settings is not possible to set.

It was working default settings.

Try1.After the boot up. We tried re-reset but it still not work phy(timeout). It seems that is working with default settings.

Try2.We set the register 420ms later after the reset but it was same result. Original wait time is 210ms.

Is there linitaion of the reset_N rise time?

Regards,

Kosaka

Hello Kosaka,

It looks like PHY is getting stuck somehow during boot-up and it is strange that even reset toggling can not recover it. Did you get the supply ramp snapshots? Something is going on at the PHY interface that is not coming out clearly from the present data. From the current data we dont see any problem with resetn signal but if making resetn faster is solving this issue then you may go for it as the faster reset waveform is also ok.

--

Regards,

Vikram

Hello Vikram,

Supply condition is same. Diffrent point is only reset ramp. It seems that LAN function is working. MDI IF is not work.

May TI highlight reset signal ramp?

And TI check the LSI logic?

Regards,

Kosaka

Hello,

With current data (as mentioned earlier) we dont see a problem. If further debug is required, you can get the snapshots of supply ramp up along side reset? Otherwise you can use the reset as described to be working in your applicaiton.

Hello

Is there concerning point?

If it need a delay time from supply ramp up timing, may we have these time spec?

Regards,

Kosaka

Hello,

Supply waveforms are ok. I dont see any glitch or non-monotonic behaviour on them. Also I noticed that resetn is toggling very close to supply getting stable, so resetn should not have impacted the PHY as in this period PHY is under reset due to internal power on reset. So it does not look like that resetn can directly impact the PHY. Are we sure that the resetn's not because of something else on the board? Example : is resetn also going to the SoC which is reading the PHY registers?

--

Regards,

Vikram

It is same condition from SOC read too. Diffrent point is only the Reset_N rise time.

How much rise time tested in TI? or May TI simulated our rise time?

Regards,

Kosaka

Hello

Is there some requierment the reset_N rise timing from supply stable? We would like to turn it.

Regards,

Kosaka

Hello,

Unfortunately there is no timing constraint that I can attribute this problem to. Moreover you have toggled resetn later also and you could not recover the bad register read/writes.

You may refer to table 7.6 and 7.7 of the datasheet for timing constraints during power-up/ reset.

Do you mean that SoC is also using the same reset net? If yes, can it be the problem with SoC who is reading the registers?

--

Regards,

Vikram

Hellow,

Soc outputs reset signal for Phy. When we change the SOC boot timing,it can read it.

So This resolved my issue.

Thank you for cooperation.

Regards,

Kosaka