Part Number: SN65DP159

Other Parts Discussed in Thread: TS3USB221, TPS60151

Hello we have designed a PCI card with two DVI interfaces.

The HDMI signals are generated by an FPGA and they are conditioned using the retimer SN65DP159.

Most card work properly, i.e.: both interfaces provide correct TMDS signals and the monitor displays the image.

In some case, after a period where the card works, one of the two interfaces stops working.

It seems like the retimer stops forwarding the TMDS signals coming from the FPGA.

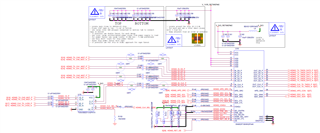

The two circuits are apparently the same, as shown below

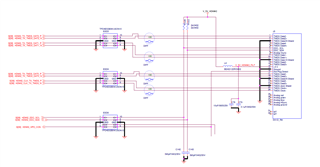

The two DVI interfaces are both sent to two independant DVI connectors, whose scheme is below

In all failure cases the broken interface s always the same, i.e.: the retimer U8.

See also below a detail of the gerber of U8.

Do you have any hint about where to focus?

Many thanks

Andrea