Hello

I’m Sanskar Verma, And I’m facing issues while developing a product using TCAN4550 for CAN-FD.

I am able to transmit and receive data with a delay of 1000 ms but if i am lowering the delay to 100 ms or below, all data packets don't reach the receiver. There is a significant loss of data while transmitting with a delay of less than 100ms.

I am able to receive all the data if there is a delay of 1000ms or more in CAN_Transmit. but my application demands no delay in transmission. I want to continiously transmit and recieve data from multiple nodes.

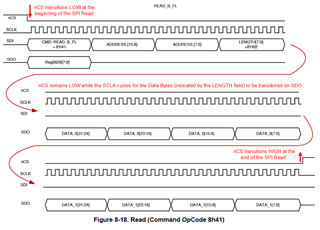

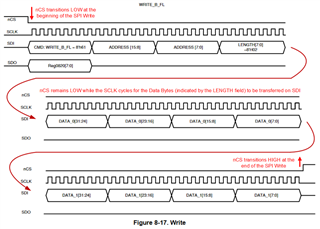

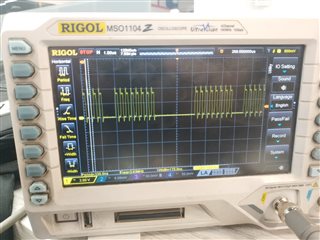

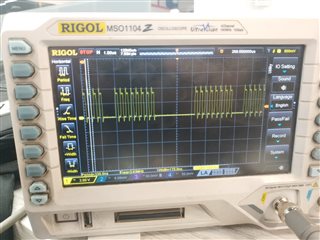

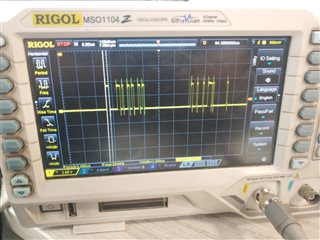

i'm attaching the all the 4 waveforms of SPI communication and the values of the registers 0x000c, 0x820, 0x0824, 0x0830 for your reference. Please look into it and let me know if you want any more information from my side.

nCS

nCS

CLK

CLK

MISO

MISO

MOSI

MOSI

Values of registers

0x000C = 30000a / 20000a / 8 / 804000e (these values keep fluctuating randomly)

0x820 = 88 / 8a (these values appear mostly)

0x824 = 10105

0x830 = 809628ff

0x0800 = c84004a0