Part Number: TCAN4550-Q1

Other Parts Discussed in Thread: TCAN4550

Hi team,

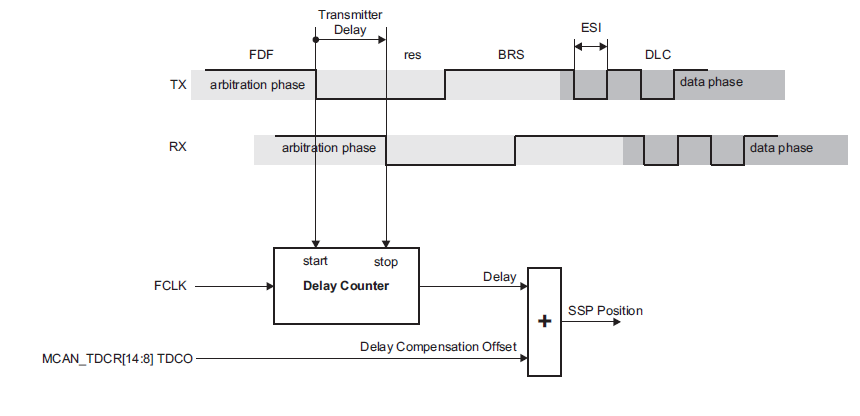

For TCAN4550-Q1, customer is confused on how to adjust secondary sample point? It seems TDCV is read only. does it mean SSP of TCAN4550 can't be adjusted by customer?

Can you please clarify the relationship between TDCV, TDCR, TDCO and TDCF? thanks!