Hi,

Below picture is my board hardware design,

For DS90UB954/953, DS90UB936/935 application, to transfer I2S signal, I found the document

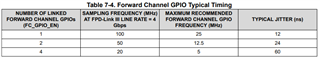

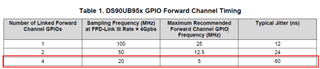

The document shows when using 4Gbps line rate, the Maximum Recommended Forward Channel GPIO Frequency (MHz) is 5MHz.

So if I use 2Gbps line rate, will the Maximum Recommended Forward Channel GPIO Frequency (MHz) be 2.5 MHz?

The SCK clock of my application is 2.048 MHz, we want to know if it's ok for 2Gbps line rate.

Thanks.