Hi team

Customer wants to understand 7.10 RGMII Timing on the datasheet. Could you support?

1. Do they need to create a PCB layout to meet 7.10 RGMII Timing?

2. Does 7.10 RGMII Timing vary with VDDIO voltage (1.8V/2.5V/3.3V)?

3. Timings as below are for MAC interfaces?

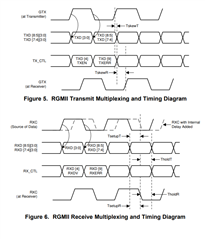

TskewT Data to Clock output Skew (at Transmitter)

TsetupR Data to Clock input Setup (at Reciever – internal delay)

TholdR Clock to Data input Hold (at Receiver – internal delay)

4. Do these timings as below guarantee a setup and hold of 1.2ns(min) for delayed RXC rising/falling?

TsetupT Data to Clock output Setup (at Transmitter – internal delay)

TholdT Clock to Data output Hold (at Transmitter – internal delay)

Regards,

Noriyuki Takahashi