Hi Ti engineer,

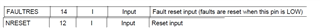

1. What is the difference between FAULTRES and NRESET? When to use FAULTRES and when to use NRESET?

2. How to use FAULTRES and NRESET? FAULTRES, NRESET Low active? What is the minimum duration of low level? Recommended reduction time?

3. If PGA411 needs to be reset during power-on, how should the timing be handled?

4.After power-on initialization, both the main chip and PGA411 have completed the reset self-check. Can the reset times be increased? Is there any harm in that?