Part Number: TPS65987D

Other Parts Discussed in Thread: TUSB8041A,

Hi team,

We are running into an issue in our application configuring the PD controller via I2C.

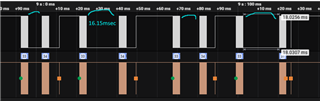

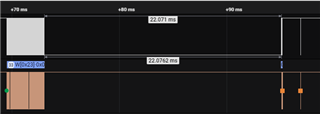

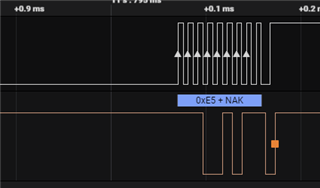

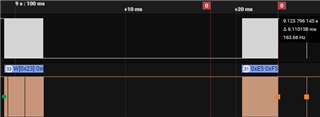

Every now and then the device fails to ACK on I2C message. This happens when sending long packets. The moment this fails is not stable.

In our I2C implementation we need to use buffers which causes moments of static I2C bus. It seems that this instability is related to the number of static periods & lengths on the bus.

An I2C bus should be able to handle infinite static periods, an SMB bus has a time out. We can reproduce this behavior on the TUSB8041A which is specified as an SMB bus. If we manipulate our I2C communication to have less 'gaps', stability improves. If we manipulate I2C communication to have longer gaps stability decreases.

We also tried other things to investigate stability such as I2C speed, temperature, swapping boards and power up sequence. No relation with this could be found.

In the TRM and datasheet, there is a single place where it says a figure is copied from SMB specification. The content in this figure is common for I2C and SMB.

Can you confirm that there is an SMBbus (I2C with time-out) implemented in the TPS65987D?

If so do you have any specification on these time outs?

Kind regards,

Mark