Other Parts Discussed in Thread: DP83869

Hi,

I am using DP83869 Phy along with Artix 7 FPGA . The LAN is not communicating with the PC. The IC is configured in MII mode. The Tx Clock is having only 100mV swing. The details are given below.

-

The DP83869 is used in MII mode.

-

VDDIO voltage used is 3.3V and the IC is used in 2 supply mode. 1.8V supply is not connected.

-

MDIO is pulled up with 2.5k ohm resistor

-

The voltage at 11k Rbias resistor is 1V

-

After power up the reset is held low for 201ms

-

Then the registers are configured as follows:

-

0x01DF0060

-

0x00005100 (10 Mbps MII loopback)

-

0x00105048

-

0x00090800

-

-

The registers are written with 34 clock cycles with first and last bit as high impedance.

-

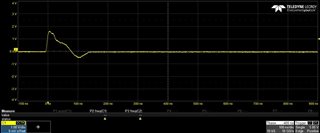

Once programmed I am getting Rx clock as 2.5 MHz with 3.3V (Pk-Pk). Tx Clock is 2.5 MHz but swing is only 100mV.

-

When connected to PC the link is not getting through.

-

When checked at the output of the magnetics, 10Base-Te Link Pulse is detected. Auto-Negotiation FLP is also detected. Screenshots of Link pulse and FLP attached.

-

The LAN connector used on the PCB is a circular connector, 801-023-07M7-10SA (Mighty Mouse). One end of the LAN cable has the mating connector for the circular connector and the other end of the cable is an RJ45 connector which is connected to the PC. The connection from circular connector to RJ45 is as per the attached wiring diagram recommended for 568B.

Phy Circuit Diagram:

Magnetics Schematic:

Phy Tx Clock:

Phy Rx Clock:

Phy Output Clock:

Link Pulse:

Auto Neg FLP:

Kindly let me know whether I am missing anything in the design.

Thanks & Regards,

Shafna