Part Number: THVD8000

Hi,

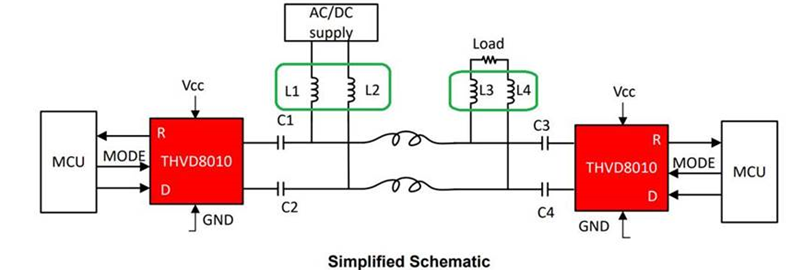

Good Day. Customer is using the THVD8000 EVM evaluation board. He wants to connect a DC power supply to the VBB and GNB pins to send power on the line. However, the C10 and C6 in the schematic are rated for 50 and 25 V. What is the maximum DC voltage source that he can connect? Please advise. Thank you very much.

Best Regards,

Ray Vincent