I have a new design, first time using the DP83867CR device. I am seeing RxDV pulses on the other end of my connection (older pcb with a different phy) that I do not expect. In other words, on the DP83867CR I am not setting the TxEn bit to start a transfer, but the other end seems to think it is receiving a transfer.

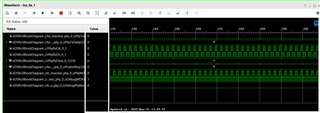

On the DP83867 I have cleared the auto-negotiate bit in the BMCR register, as well as set my desired speed (100 Mbps). If I loopback the cable I see the appropriate RX Clock, so I believe my BMCR settings 'took'. Loopback mode also shows RxDV traffic only when I am sending traffic (TxEN going high).

I also cleared all bits in CFG1 (I'm not sure this is necessary since I am not in 1000Base-T mode).

In addition, our design did not appropriately strap RxDV on the DP83867CR, so I also did the indirect memory addressing to clear bit 7 of CFG4.

This design is fpga-based on both ends (new board with DP83867CR) and older board, and the unexpected traffic is causing problems with the old board trying to process this traffic.

I have looked at all of my writes to the MI (BMCR, CFG1, indirect addressing of CFG4) and they look correct, but since the design is fpga-based it is difficult to read the status registers to confirm everything.

Any ideas on if I have missed additional strapping or configuration register setting is appreciated!