Hi everyone,

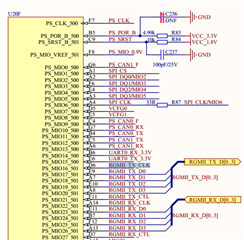

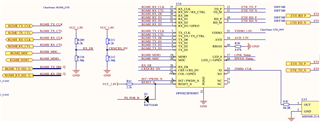

I have a customzied Xilinx Zynq-7000 board with TI DP83822IFR PHY chip. We are using PS7 GEM on Zynq as ethernet controller and operates in rgmii mode, 100Mbps.

I am testing MII Loopback mode of TI PHY chip. I configured DP83822 as following:

- Write 0x4000 into the PHYRCR register(0x001F): active software reset.

- Write 0x8000 into the BMCR register (0x0000): initiate PHY reset

- Write 0x6100 into the BMCR register (0x0000):enable MII Loopback mode and set the speed: 100 Mbps - full duplex

- Transmit packets from MAC to DP83822 PHY.

- Wait for Rx indication in MAC.

But I cannot receive any packet in MAC.

Does anyone know what I missed or I need to do to test MII Loopback between Xilinx Zynq and TI DP83822 successfully ?

I also attach my schematic. I am wondering whether my hardware design has any problems ??

By the way, I am confusing about Phy Address value. Because RX_D[3:0] pins of TI PHY is not connect to any pull-up/pull-down resistor as attached schematic, PHY_AD[4:1] should be 3'b000, and Phy Address should be 1.

But I detected Phy Address is 31 (PHY_AD[4:1] = 3'b111).

Could anyone explain about it for me, please ?

Thanks in advance !!

Best Regards,

Dat Phung