Part Number: DP83867E

Hi Team,

Good evening,

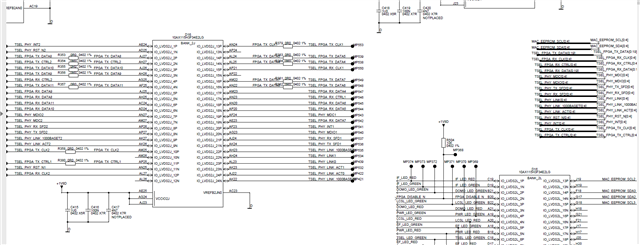

We need your support urgently on the TI - DP83867 Bring up issues. We are using the Arria10 Intel chipset FPGA to interface with TI PHY chip.

We have captured the signals during the bring up. Please go through the captures and suggest the debug instructions if we miss any (Captures shared with Shinu Mathew vmshinu@ti.com in mail)?

Also, we are unable to make MDIO register access. My Team said that NIOS software is used and they are not familiar with MDIO register access. It will be great if you have any inputs on how to access MDIO registers will be of great help.

Best Regards

Srikanth