Hi Team,

Some DSI bridge questions as below, please help. Thank you.

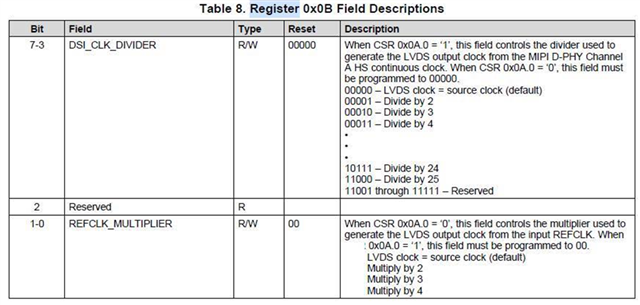

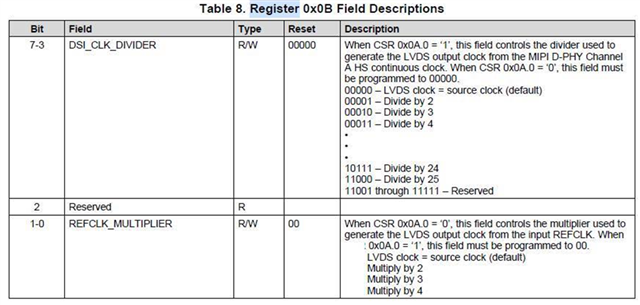

1. How to decide this REG 0x0B DSI_CLK_DIVIDER setting parameter?

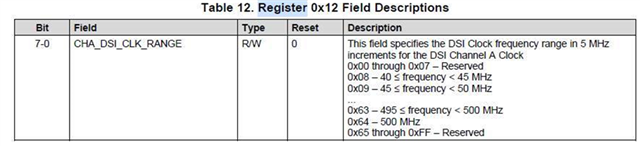

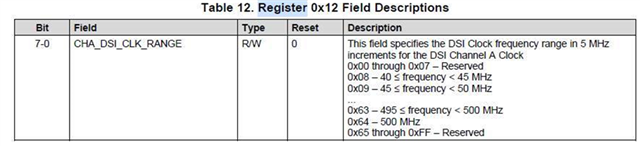

2. How to decide this REG 0x12 parameter?

3. Does the chip have SSC function?

Regards,

Roy

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Team,

Some DSI bridge questions as below, please help. Thank you.

1. How to decide this REG 0x0B DSI_CLK_DIVIDER setting parameter?

2. How to decide this REG 0x12 parameter?

3. Does the chip have SSC function?

Regards,

Roy

Roy

For question 1 and 2, please use this tool to generate the programming value for register 0x0B and 0x12 as the value depends on the input reference/DSI clock and required LVDS output clock.

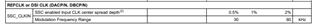

For question 3, SSC can be supported only if the source CLK is provided with SSC.

Thanks

David

Hi David,

We meet EMI issue about LVDS clk. We used MIPI CLK instead of REFCLK and couldn't enable the SSC function.

Do you have any countermeasure about the LVDS CLK noise? Thank you.

Regards,

Roy

Roy

They can improve layout for better impedance discontinuity as laid out in this app note, https://www.ti.com/lit/an/snla302/snla302.pdf.

They can also add common mode filters if they can, https://product.tdk.com/system/files/dam/doc/content/emc-guidebook/en/eemc_practice_03.pdf.

Or they can switch to a ref clock that can support SSC.

Thanks

David