Part Number: DS90UB954-Q1

Hi team,

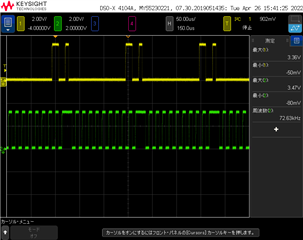

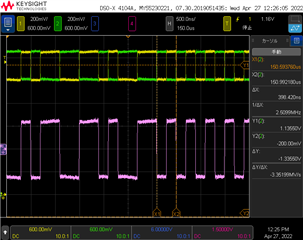

What are the conditions under which the LOCK pin of the 954 goes Hi?

Does LOCK go Hi unless parallel data is input to 933?

The situation now is as follows.

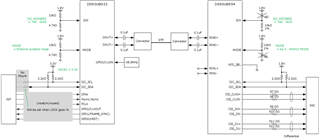

The 933 and 954 are powered and PDB is Hi.

They are connected by STP cable and register 0x0C of 933 is confirmed to be 0x01.

The mode setting of 933 is 10-bit mode.

The mode setting of 954 is set as CSI-2 non synchronous Back Channel at the pin, but is changed to RAW10 by I2C.

VDD_SEL of 954 is Lo, and the register setting is as shown in the table below.

| Address | Setting Value |

| 0x0C | 0x81 |

| 0x0D | 0x09 |

| 0x18 | 0x01 |

| 0x19 | 0x00 |

| 0x1A | 0x02 |

| 0x1B | 0x0A |

| 0x1C | 0xE6 |

| 0x1F | 0x02 |

| 0x20 | 0x30 |

| 0x21 | 0x01 |

| 0x32 | 0x00 |

| 0x33 | 0x21 |

| 0x4C | 0x01 |

| 0x58 | 0x58 |

| 0x5C | 0xB4 |

| 0x6D | 0x7B |

| 0x70 | 0x1E |

| 0x71 | 0x2C |

| 0x72 | 0x00 |

| 0x7C | 0xC1 |

| 0xBC | 0x00 |

best regards.