Definitions:

TX_DATA[3:0], TX_CLK (naming of TI Ethernet PHYs) are transmitted by the MAC/(Repeater PHY) and RX_DATA[3:0], RX_CLK (naming of TI Ethernet PHYs) are transmitted by Ethernet PHY.

| S.No | Mode | Definition |

| 1 | PHY: RX Align Mode | PHY transmits RX_DATA[3:0] with no delay w.r.t RX_CLK |

| 2 | PHY: RX Shift Mode | PHY transmits RX_DATA[3:0] with programmable delay w.r.t RX_CLK |

| 3 | PHY: TX Align Mode | PHY introduces no delay on TX_CLK w.r.t TX_DATA[3:0] before sampling |

| 4 | PHY: TX Shift Mode | PHY introduces programmable delay on TX_CLK w.r.t TX_DATA[3:0] before sampling |

| 5 | MAC: RX Align Mode | MAC introduces no delay on RX_CLK w.r.t RX_DATA[3:0] before sampling |

| 6 | MAC: RX Shift Mode | MAC introduces delay on TX_CLK w.r.t TX_DATA[3:0] before sampling |

| 7 | MAC: TX Align Mode | MAC transmits TX_DATA[3:0] with no delay w.r.t TX_CLK |

| 8 | MAC: TX Shift Mode | MAC transmits TX_DATA[3:0] with delay w.r.t TX_CLK |

Disclaimer: The nomenclature described above is what is used by TI PHY. The terms can be different from what other PHY vendors and MAC vendors use.

Meeting RGMII Timing:

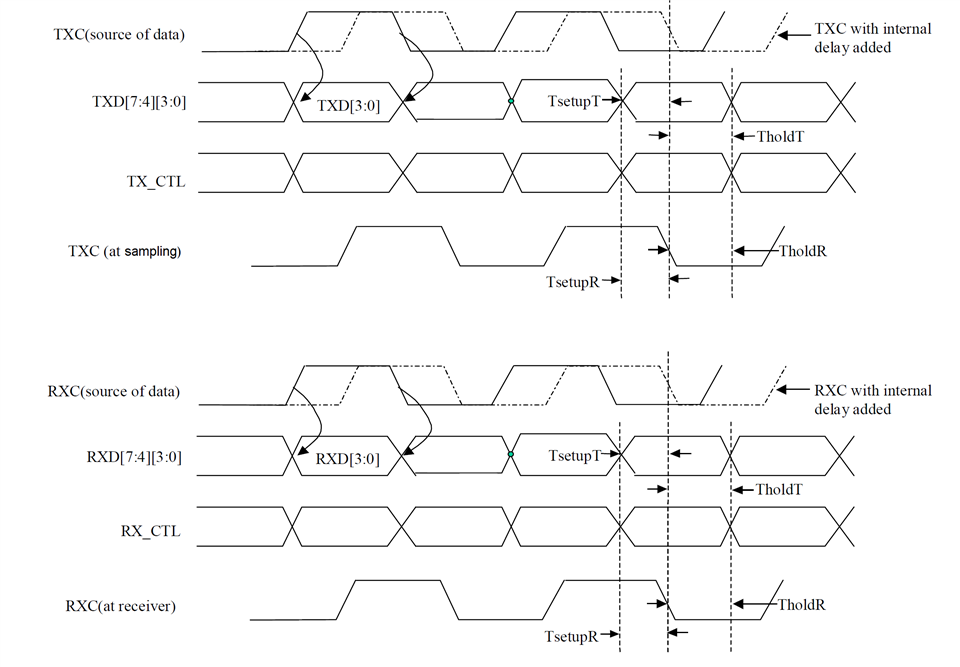

When the TX_DATA[3:0] is sampled by Ethernet PHY w.r.t TX_CLK, a delay is needed between rise/fall edges of TX_CLK and TX_DATA[3:0] to meet Tsetup and Thold.

This delay can be implemented by

Method-1: Increase the propagation delay by routing TX_CLK on the PCB longer.

Method-2: Let MAC transmit TX_CLK with an internal delay w.r.t TX_DATA (TX shift mode - MAC)

Method-3: Let PHY introduce an internal delay on TX_CLK w.r.t TX_DATA before sampling ( TX shift mode - PHY)

Similarly when RX_DATA[3:0] is sampled by the MAC w.r.t RX_CLK, a delay is needed between rise/fall edges of RX_CLK and RX_DATA[3:0] to meet Tsetup and Thold.

This delay can be implemented by

Method-1: Increase the propagation delay by routing TX_CLK on the PCB longer.

Method-2: Let PHY transmit RX_CLK with an internal delay w.r.t RX_DATA (RX shift mode - PHY)

Method-3: Let MAC introduce an internal delay on RX_CLK w.r.t RX_DATA before sampling ( RX shift mode - MAC)

Illustration below shows the timing diagram of PHY TX and RX Shift mode.

For method-2 and method-3, only the following combinations are allowed

| S.No | PHY mode | MAC mode |

| 1 | RX Align | RX shift |

| 2 | RX Shift | RX Align |

| 3 | TX Align | TX Shift |

| 4 | TX Shift | TX Align |

The delays in shift mode are programmable (through straps or registers) and to be chosen accordingly to meet TsetupR(T) and TholdR(T).