Hi.

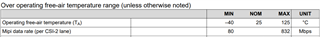

I found difficulty when I try to understand those concepts as title. let me take 953 as example. we can get that from datasheet as below:

here is my questions:

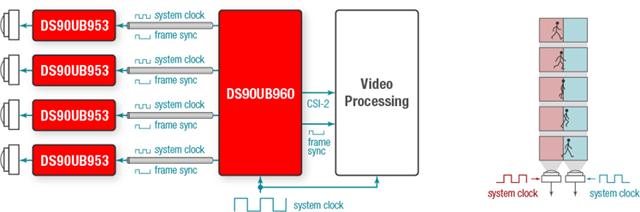

- when we talked about video aggregation size, are we talking CSI bandwidth? like for 953, the maximum video aggregation side is 832M*4=3.33Gbps, right?

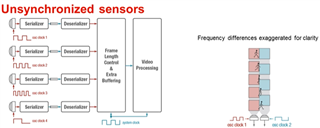

- when we talked about what kind of imager device can support, are we also limited by video aggregation size/CSI bandwidth? from the datasheet, the long packet CSI-2 has 40bit per frame. so for 2.3MP 60fps imager, it need 2.3M*60*40=5.5Gbps without blanking which is beyond 3.33G or 4.16Gbps. where is wrong?

- when we talked about 4.16Gbps, are we talking the FPDLINK3 forward channel line rate? from the table as below, why the FC data rate is always larger than CSI bandwidth?

thank you!

B&R

Yuan