Other Parts Discussed in Thread: DP83869,

We are considering DP83869 for a 1000BASE-X (fiber) application. We are looking for more info on using the GPIO lines to indicate SFD on RX and TX for IEEE 1588 synchronization.

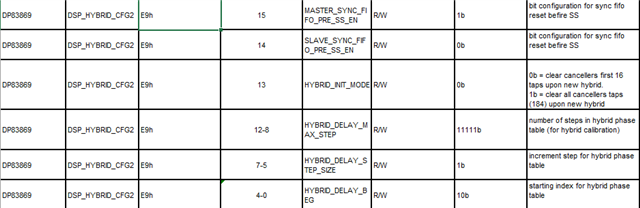

On page 25 of the datasheet where it discusses this functionality, it says "Before a link is established in 1000-Mb mode, the Sync FIFO Control Register (register address 0x00E9)

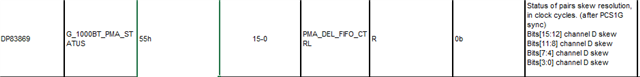

must be set to value 0xDF22". On page 26 it also says " When the DP83869HM is operating in 1000-Mb master mode, variation of the RX_SFD pulse can be estimated

using the Skew FIFO Status register (register address 0x0055) bit[7:4]".

But neither 0x00E9 or 0x0055 are listed in the register maps in section 9.6. Where can we find more info about registers 0x00E9 and 0x0055?