Part Number: DS90UB928Q-Q1

Hi team,

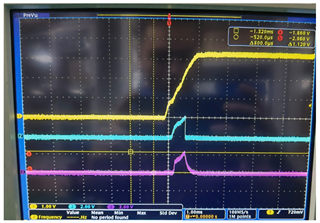

As you can see in the below figure, the GPIO2&3 has a short time high level. Could you kindly tell me what is the reason?

Channel 1: VDDIO&VDD33

Channel 2: GPIO2

Channel 3: GPIO3

BR

Jiawei

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: DS90UB928Q-Q1

Hi team,

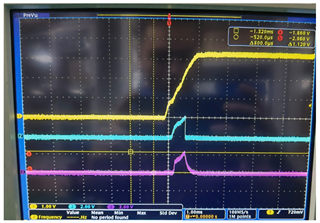

As you can see in the below figure, the GPIO2&3 has a short time high level. Could you kindly tell me what is the reason?

Channel 1: VDDIO&VDD33

Channel 2: GPIO2

Channel 3: GPIO3

BR

Jiawei

Hello Jiawei,

This looks like a result of having the VDDIO and VDD33 tied together. As the supplies are initially ramping, the I/O inside the device is not biased, so there is leakage from the VDD33 rail through to the GPIOs. Once the VDDIO reaches a higher level, then the I/O is sufficiently biased and the pins will have a weak pulldown to GND. Think should not lead to any issues with the part as VDD33+VDDIO supply from the same power rail is allowed within the datasheet.

Best Regards,

Casey