Part Number: DS90UB936-Q1

Hi, Team,

Our setup is 935 + 936, and we plan to use 3 GPIOs from host to control ub935 GPIO output via ub936.

One of our GPIO design is

host GPIO6 -> ub936 GPIO6 -> ub935 GPIO0

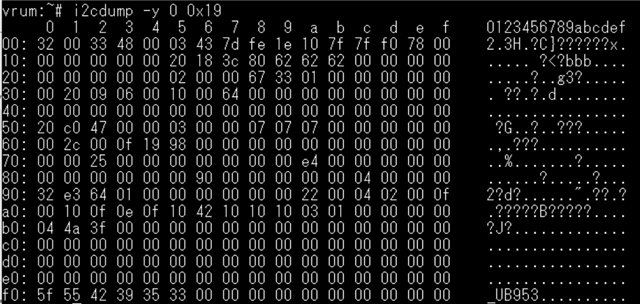

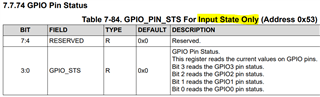

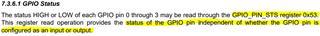

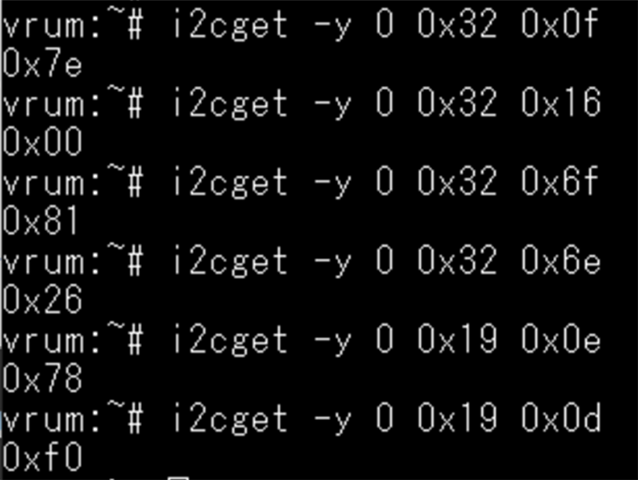

Some related configure in below.

When we set host GPIO6 to 1, then ub936 GPIO6 state is 1

![]()

But UB935 side GPIO0 still is 0.

![]()

Why UB935 GPIO_0 can't be set to 1?

Thank you,

--Blake