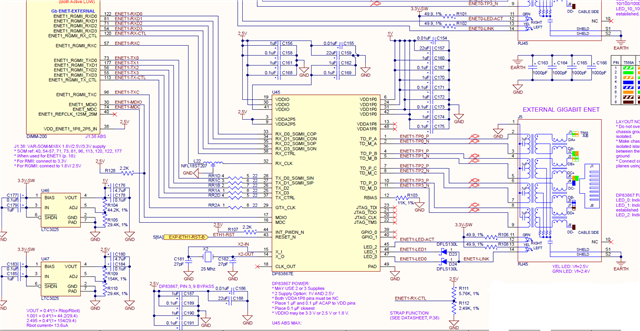

Part Number: DP83867E

Greetings,

Currently debugging yocto based embedded system using DP83867E for our Phy.

I am able to communicate with the phy through MDIO, doing a register dump I get the following in u-boot:

=> mii dump 0 0-a

0. (1140) -- PHY control register --

(8000:0000) 0.15 = 0 reset

(4000:0000) 0.14 = 0 loopback

(2040:0040) 0. 6,13 = b10 speed selection = 1000 Mbps

(1000:1000) 0.12 = 1 A/N enable

(0800:0000) 0.11 = 0 power-down

(0400:0000) 0.10 = 0 isolate

(0200:0000) 0. 9 = 0 restart A/N

(0100:0100) 0. 8 = 1 duplex = full

(0080:0000) 0. 7 = 0 collision test enable

(003f:0000) 0. 5- 0 = 0 (reserved)

1. (7949) -- PHY status register --

(8000:0000) 1.15 = 0 100BASE-T4 able

(4000:4000) 1.14 = 1 100BASE-X full duplex able

(2000:2000) 1.13 = 1 100BASE-X half duplex able

(1000:1000) 1.12 = 1 10 Mbps full duplex able

(0800:0800) 1.11 = 1 10 Mbps half duplex able

(0400:0000) 1.10 = 0 100BASE-T2 full duplex able

(0200:0000) 1. 9 = 0 100BASE-T2 half duplex able

(0100:0100) 1. 8 = 1 extended status

(0080:0000) 1. 7 = 0 (reserved)

(0040:0040) 1. 6 = 1 MF preamble suppression

(0020:0000) 1. 5 = 0 A/N complete

(0010:0000) 1. 4 = 0 remote fault

(0008:0008) 1. 3 = 1 A/N able

(0004:0000) 1. 2 = 0 link status

(0002:0000) 1. 1 = 0 jabber detect

(0001:0001) 1. 0 = 1 extended capabilities

2. (2000) -- PHY ID 1 register --

(ffff:2000) 2.15- 0 = 8192 OUI portion

3. (a231) -- PHY ID 2 register --

(fc00:a000) 3.15-10 = 40 OUI portion

(03f0:0230) 3. 9- 4 = 35 manufacturer part number

(000f:0001) 3. 3- 0 = 1 manufacturer rev. number

4. (0181) -- Autonegotiation advertisement register --

(8000:0000) 4.15 = 0 next page able

(4000:0000) 4.14 = 0 (reserved)

(2000:0000) 4.13 = 0 remote fault

(1000:0000) 4.12 = 0 (reserved)

(0800:0000) 4.11 = 0 asymmetric pause

(0400:0000) 4.10 = 0 pause enable

(0200:0000) 4. 9 = 0 100BASE-T4 able

(0100:0100) 4. 8 = 1 100BASE-TX full duplex able

(0080:0080) 4. 7 = 1 100BASE-TX able

(0040:0000) 4. 6 = 0 10BASE-T full duplex able

(0020:0000) 4. 5 = 0 10BASE-T able

(001f:0001) 4. 4- 0 = 1 selector = IEEE 802.3 CSMA/CD

5. (0000) -- Autonegotiation partner abilities register --

(8000:0000) 5.15 = 0 next page able

(4000:0000) 5.14 = 0 acknowledge

(2000:0000) 5.13 = 0 remote fault

(1000:0000) 5.12 = 0 (reserved)

(0800:0000) 5.11 = 0 asymmetric pause able

(0400:0000) 5.10 = 0 pause able

(0200:0000) 5. 9 = 0 100BASE-T4 able

(0100:0000) 5. 8 = 0 100BASE-X full duplex able

(0080:0000) 5. 7 = 0 100BASE-TX able

(0040:0000) 5. 6 = 0 10BASE-T full duplex able

(0020:0000) 5. 5 = 0 10BASE-T able

(001f:0000) 5. 4- 0 = 0 partner selector = ???

9. (0300) -- 1000BASE-T control register --

(e000:0000) 9.15-13 = 0 test mode

(1000:0000) 9.12 = 0 manual master/slave enable

(0800:0000) 9.11 = 0 manual master/slave value

(0400:0000) 9.10 = 0 multi/single port

(0200:0200) 9. 9 = 1 1000BASE-T full duplex able

(0100:0100) 9. 8 = 1 1000BASE-T half duplex able

(0080:0000) 9. 7 = 0 automatic TDR on link down

(1fc0:0300) 9. 6 = 12 (reserved)

10. (0000) -- 1000BASE-T status register --

(8000:0000) 10.15 = 0 master/slave config fault

(4000:0000) 10.14 = 0 master/slave config result

(2000:0000) 10.13 = 0 local receiver status OK

(1000:0000) 10.12 = 0 remote receiver status OK

(0800:0000) 10.11 = 0 1000BASE-T full duplex able

(0400:0000) 10.10 = 0 1000BASE-T half duplex able

(0300:0000) 10. 9- 8 = 0 (reserved)

(00ff:0000) 10. 7- 0 = 0 1000BASE-T idle error counter

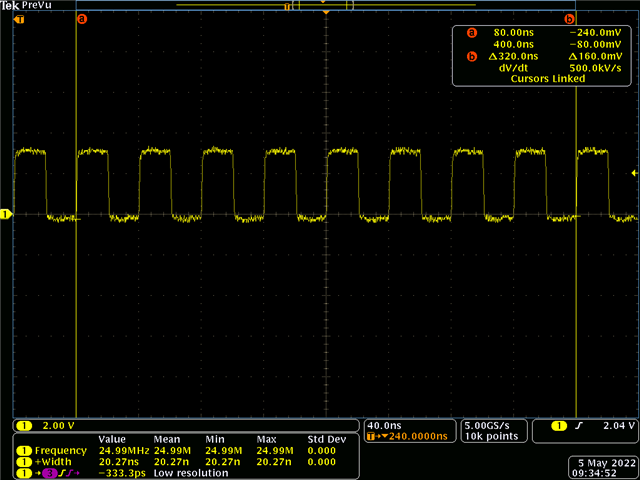

Looking at td_a_p and td_p_b I can see the keep alive pulse but nothing else when I connect rj45 cable.