Other Parts Discussed in Thread: ALP

Hi Team,

Would like to know if I want to generate below input signal from 949 to 948.

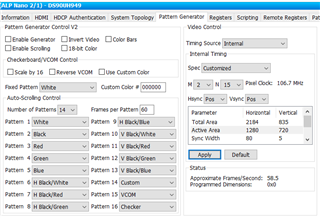

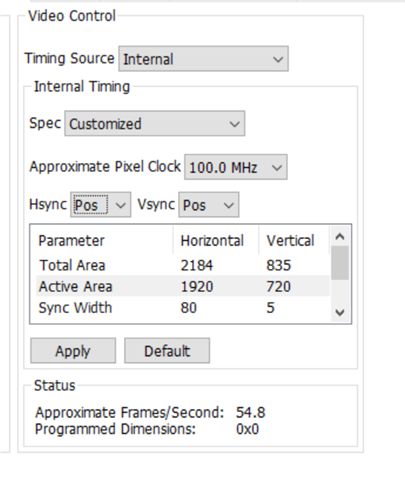

how should I set the register on 949? (by using Analog LaunchPAD)

PCLK:109.42 MHz (external clock from pulse generator)

Active size:1920H x 720V

Total size: 2184H x 835V

Regards

Tommy