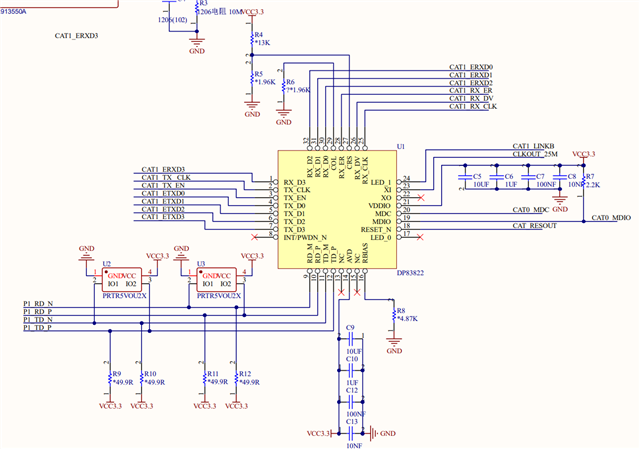

Part Number: DP83822I

Hi Team

Good day, and hope this email finds you well.

I’m reaching out because my customer XINJE have some question about our DP83822I.(The application is in HMI(human machine interface))Could you please help me about these issue?

- They want to run it in the 100M Full-Duplex Mode (MII mode), but there is something wrong : The register flag bit-- Auto-Negotiation Complete (0X001.5) has always been 0, indicating that the chip auto-negotiation has not yet been completed. Is this issue related to their resistor configuration? Please kindly receive the attachment of their schematic.

2.The register marker bit--- SMI Preamble Suppression (0x0001.6) is 1, and according to the manual, the chip appears to remove the Preamble during normal operation. However, XINJE usage scenario requires that this Preamble must be retained, so they wanted to consult how to modify the configuration of this aspect. The register value of the 0x00 to the 0X1F is attached please received.

3.COL/CRS is not required in the their case of ethercat, but how to configure it does not affect the normal operation of the PHY chip. I find the COL is default disable, so disable the COL doesn’t need to special configuration. But I didn’t figure out how to disable CRS.

4. In the MII mode, if they left the RX_D2/RX_D3/TX_D2/TX_D3 floating, will it affect to normal function?

5.They found that if the 3.3V was build after the DP83822 start, the Auto-Negotiation won't success, even if the 3.3V was build, the Auto-Negotiation still not success.

This is the first time they use DP83822 in XINJE’s HMI. I’ll really appreciate it if you have any clue about their questions.

Thanks