Other Parts Discussed in Thread: ALP

I originally posted the following comment in the thread below, but was asked to make a new topic. Some of the syntax is referencing the previous thread.

I am experiencing a very similar problem with the DS90UB954 & DS90UB953 link.

I have not been able to determine why it happens yet, but it is not associated with address or register offset.

I do not know what the default BCC timeout is for your parts, but on on the 954/953 setup it is 254msec.

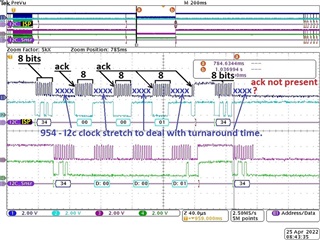

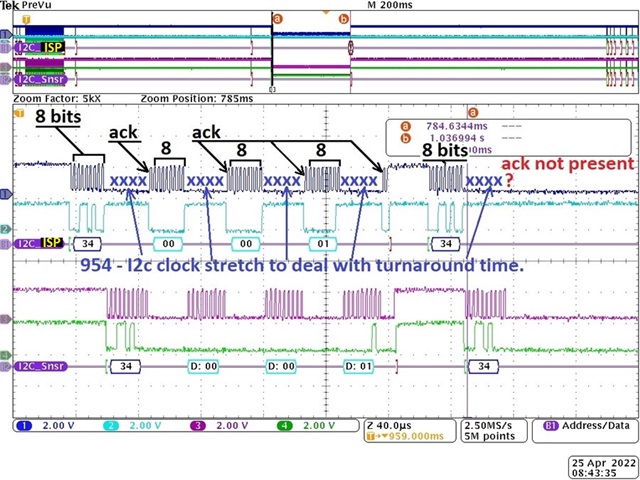

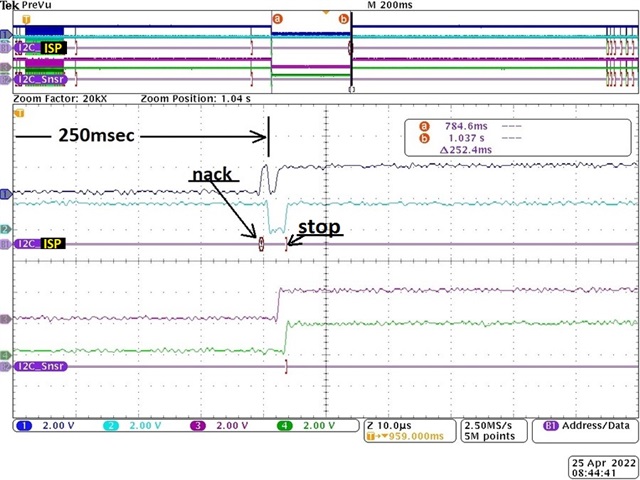

The upper portion of the initial scope capture shows the ISP to 954 waveform of a successful boot process. The bottom portion of the same image shows a failed waveform where the 954 did not produce an ack for the ISP's I2c write to the sensor. The time between points A & B is roughly 250msec which is the default value of the 954 BCC timeout.

The next scope capture shows a closeup of the beginning of a failed write (point a in the upper part of the capture). You can see a good write cycle consisting of a 7bit (write) address, 16bit register offset, and 8bit data. For each 8bit cycle you see the acks present after the clock stretch which happens while waiting for the 953 & sensor to finish. In the address portion of the next 4 byte write cycle the 954 does not produce the required ack to the ISP, but you can see that the ack "was produced" by the sensor to the 953.

The final scope capture shows a closeup of the end of the same failed write cycle (point b in the upper part of the capture). The 954 normal process when a BCC timeout happens is for it to issue a nack which then will allow the Master to issue a stop for the cycle. This is exactly what is seen in the capture.

I have not been able to determine why it happens yet, but it is not associated with address or register offset.

I do not know what the default BCC timeout is for your parts, but on on the 954/953 setup it is 254msec.

You can see that the required signal protocol works through the write, but it fails in getting the sensors' ack back to the ISP from the 954.

Justin, I am re-entering your last comment in the other thread below so I can add my answer and it not be lost.

*******************************

Hello David,

In the FPD-Link devices, when the a Master sends an I2C command from Master->DES->SER->Slave, the target Slave needs to send an ACK response back to the Master over the cable link between the SER and the DES.

drc: you can see in the waveforms that the target Slave "does" ack the 953 in all cases.

An 8-bit I2C address is sent to the Slave first. If the Slave responds with a proper ACK, then the Master will send another 8-bit message which is the actual READ/WRITE command. It seems to me that when an I2C message is sent from the Master->Slave, the wrong address is used and there is no Slave that matches the address. As a result, no Slave will send an ACK response back to the Master and the Master will not send an 8-bit I2C READ/WRITE command. The Watchdog Timer on the SER will automatically cancel the I2C action after some time if no ACK bit is sent back.

drc: I believe you see the 7-bit address and write bit from the Master, to the 954, through the coax, out from the 953, to the image sensor happening and the image sensor correctly responding with the ack. After the address you also see the 16bit register offset and then the 8bit data to be written. All 4 cycles show the image sensor producing the required ack.

drc: In response to your description I have the following - If the Master issues a write to an address that is not present on the bus the data line will be high (because of the pullup) and the Master will still be able to generate its' clock (since there is no Slave to hold the clock line low) which will produce a nack. This is a normal I2c cycle which indicates the Slave address is not present and it "will not" produce a BCC timeout.

Here are also some App Notes that describe the topic, when including the FPD-Link devices:

Best,

Justin Phan

**************************************

I am open to any ideas on what this failure is from.

thank you,

david