We are experiencing same issues as described on

and

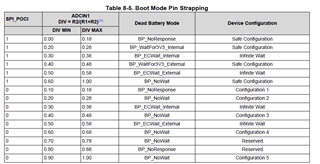

Does anyone in the course of the last three years analyzed what exactly, on some specimens, tickles wrong the ADCIn1/2 inputs when they are tied directly (via a resistor) to LDO_3V3? We are now following the advice given on both threads of 10KΩPU/100KΩPD and the situation seems to be fixed, but are not necessarily fully confident that those values are adequate as we don't understand the physics that are at play in this "singularity" phenomenon.

Further uneasiness is brought about the fact that the latest TPS65987DDJ EVM (SLVUBS4A) shows on that the ADCIn1 divider is to be 31.6KΩPU/100KΩPD.

Please kindly explain reason for the singularity and how much the voltages (i.e. divide ratio) on ADCIn1/2 have to be reduced below LDO_3V3 to guarantee that this issue never happens.

Thanks so much!

Georg A. Mussenden